© JTAG Technologies

Elektronikproduktion |

Update von JTAGs Visualizer mit neuen Features für schnelleres Debugging

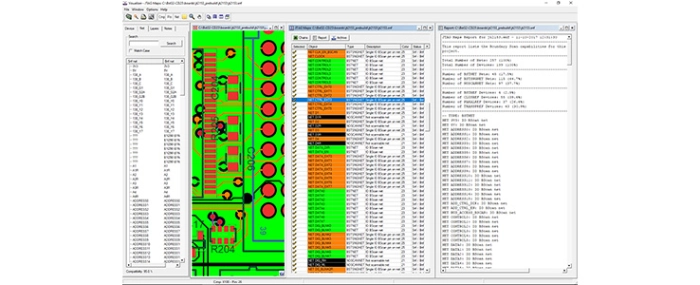

JTAG Technologies veröffentlicht eine neue Version des JTAG Visualizers – einem beliebten grafischen Tool zur Anzeige von Leiterplattenlayout und Schaltplan.

Das ist eine Produktankündigung von JTAG Technologies. Allein der Emittent ist für den Inhalt verantwortlich.

Dem Anwender erlaubt die Software eine einfache Anzeige der Fehlerabdeckung und ermöglicht die punktgenaue Lokalisierung von Fehlern, welche im Produktionstest festgestellt wurden.

Umfassender Support verschiedener CAD-Systeme

Mit der breiten Pallette von Importfiltern für verschiedenste CAD Hersteller ist der Visualizer ein wichtiges Werkzeug für alle Testingenieure bei der Entwicklung von Boundary-Scan-Tests. Der Anwender kann den Schaltplan direkt aus Mentor (Pads, DxDesigner, Capture), Cadence, Altium oder Zuken importieren. Die Layoutdaten werden im ODB++ Format oder einem Dutzend weiterer anbieterspezifischer Formate eingelesen.

JTAG Maps

Neu in dieser Version des Visualizers ist das Feature “Maps”, welches eine elementare Darstellung des Boundary Scan Testzugriffs erlaubt. Dieser basiert auf der Erweiterung der Beschreibung wichtiger Bauteile in einer Lookup-Tabelle. Der Boundary Test Zugriff wird in unterschiedlichen, vom Kunden frei konfigurierbaren Farben angezeigt. Der „eingefärbte“ Schaltplan wird Ihnen direkt angezeigt und steht auch zum Ausdruck zur Verfügung. Sobald das Design bezüglich der Boundary-Scan Testabdeckung optimiert und layoutet wurde, kann mittels des Entwicklungswerkzeugs JTAG ProVision mit der Testapplikationsentwicklung begonnen werden.

Weitere neue Funktionen

Visualize on (Test) Fail – Bei der Entwicklung einer Testsequenz oder während des Testdebuggings ist es möglich sich alle fehlerbehafteten Schaltungsknoten automatisch im Schaltplan bzw. Layout anzeigen zu lassen. Gerade bei kleinen Losgrößen, bei denen der Prüfer auch für die Fehlerdiagnose und Reparatur zuständig ist, ermöglicht dieses Feature eine einfache Lokalisierung des fehlers und somit eine schnelle Reparatur.

Locate Next – Bei der Fehlersuche kann der Reparateur mit Hilfe der ‘Locate Next’-Funktion den Verlauf eines Netzknotens durch die Lagen eines Leiterplatten-Layouts oder die Seiten eines Schaltplans verfolgen.

Multiple Color Themes– Benutzer können jetzt mehrere Farbschemen zur leichten Unterscheidung verschiedener Netzklassen, definieren. Das gilt z B. für die prozentuale Fehlerabdeckung im Schaltplan oder für fehlerhafte Netze in Layout, was das Debugging und die Reparatur erleichtert.

View Through Layers – Ein markiertes, fehlerhaftes Netz, welches z.B. als eine fehlerhafte Leiterplattenverbindung erkannt wurde, kann jetzt entlang seines gesamten Verlaufs, über alle Lagenwechsel, betrachtet werden.

Add Notes – An frei wählbaren Positionen im Schaltplan oder Layout können Hinweise oder Notizen hinzugefügt werden. Sie eignen sich ideal, um zusätzliche Informationen über Testprozesse zu geben oder Designdetails mit den Kollegen auszutauschen.

„Diese beeindruckenden Verbesserungen des Visualizer-Tools sind das Ergebnis unserer engen Kooperation mit unseren Kunden und der Zusammenarbeit mit zahlreichen EDA-Softwareanbietern“, kommentiert Peter van den Eijnden, Geschäftsführer von JTAG Technologies, die aktuelle Version des Visualizer.

Ein weiteres Highlight auf der Messe : JTAGs ATE-Integration

Mit ‘ATE-Integration‘ hat JTAG Technologies ein weiteres Highlight für seine Besucher am Messestand vorbereitet, das entscheidend zur Verbesserung der Testabdeckung beiträgt.

Viele Anwender müssen die Testabdeckung für ihre bestückten Leiterplatten verbessern. Das muss nicht schwer sein. Die Lösung liegt in der Verbindung der Boundary-Scan-Tools von JTAG Technologies mit den bereits vorhandenen Testsystemen (ATE). JTAG arbeitet mit allen Herstellern von In-Circuit-Testern (ICT), Flying-Probe-Testern (FPT) und Funktionstestern (FKT) zusammen.

Die ATE-Integration ist absolut problemlos und erfordert lediglich eine Erweiterung der Anwendungssoftware für das bestehende Testsystem. In vielen Fällen bietet JTAG Technologies speziell auf das Format angepasste Boundary-Scan-Controller oder Pods zur optimalen Einbindung der Hardware. Dies vereinfacht die mechanische Integration und sorgt für höchste Signalintegrität.

Die Experten am Messestand diskutieren gerne mit den Besuchern eine optimale Integration entsprechend den Anforderungen ihres Projekts.