© AT&S

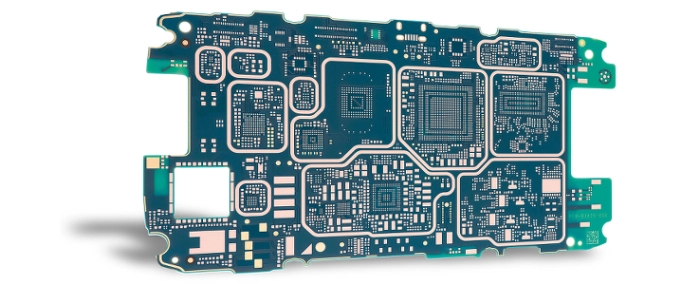

Leiterplatten |

AT&S beteiligt sich an mehreren Konsortien

AT&S beteiligt sich an wichtigen Industrie-Konsortien zur Entwicklung von GaN-Prozessen und Panel-Level-Packaging.

AT&S arbeitet seit Jahren an der Weiterentwicklung von Prozessen und Technologien bei der weiteren Miniaturisierung und den Forderungen nach verbesserter Energieeffizienz. Vor diesem Hintergrund ist das Unternehmen auch an verschiedenen Forschungs- und Entwicklungs-Programmen beteiligt. Dazu gehören aktuell das Horizon 2020 EU Research und Innovation Program, bei dem insgesamt 11 europäische Unternehmen an dem Projekt GaNonCMOS arbeiten. Außerdem wirkt AT&S an dem vom Fraunhofer IZM geführten Panel-Level-Packaging Konsortium mit.

Optimierte Energieeffizienz mit GaN

In den nächsten vier Jahren will will das Konsortium im Rahmen des GaNonCMOS-Projektes und unter Beteiligung von AT&S kostengünstige und zuverlässige GaN-basierte Prozesse, Komponenten, Module und Integrationsansätze erarbeiten. Damit sollen vor allem die Vorteile von GaN hinsichtlich der Energieeffizienz genutzt werden. Zielsetzung sind mehrere Demonstratoren mit GaN-Leistungsschaltern und CMOS-Treibern sowie neue magnetische Core-Materialien, womit Schaltfrequenzen bis zu 200 MHz erreicht werden können. Zusammen mit optimierter Embedded-Leiterplatten-Technologie soll die Entwicklung zu neuen integrierten Leistungskomponenten für kostengünstige und hochzuverlässige Systeme führen. Neben AT&S arbeiten die Katholische Universität Leuven, Epigan, Fraunhofer, IBM Research, IHP, Tyndall National Institute, PNO Innovation, Recom, NXP Semiconductors und X-FAB Semiconductor an diesem Projekt.

Fortschreitende Miniaturisierung mit Panel-Level-Packaging

Auch das Panel-Level-Packaging Konsortium ist mittlerweile gestartet. Hier kollaborieren internationale Partner wie Intel, ASM Pacific, Hitachi Chemical, AT&S, Evatec, Nanium, Süss MicroTec, Unimicron, Brewer Science, Fujifilm Electronic Materials U.S.A, ShinEtsu, Mitsui Chemicals Tohcello und Semsysco. Zusammen mit dem Entwicklungsknoten des Fraunhofer IZM soll mit dem Fan-out-Panel-Level-Packaging (FOPLP) einer der neuesten Packaging-Trends in der Mikroelektronik umgesetzt werden. FOPLP besitzt dabei ein sehr hohes Miniaturisierungspotential, sowohl im Packagevolumen als auch in der Packagedicke.

Im Rahmen der zweijährigen Laufzeit des Konsortiums sollen die aus dem Wafer-Level-Packaging bekannten Technologiebausteine auf ein großes Panelformat übergeführt werden. Technologische Basis von FOPLP ist ein rekonfiguriertes, gemoldetes Panel mit eingebetteten Komponenten und einer Dünnfilm-Umverdrahtungslage, die zusammen ein SMD-kompatibles Package ergeben. Die Hauptvorteile des FOPLP sind ein sehr dünnes, substratloses Package, der geringe thermische Widerstand und gute HF-Eigenschaften. Darüber hinaus können in die Umverdrahtungslage passive Komponenten wie Kapazitäten, Widerstände, Spulen und Antennenstrukturen integriert werden. Damit eignet sich die Technologie auch für den Aufbau von Multichip-Packages und SiPs (System-in-Package).