© Analog Devices Inc.

Application Notes |

High-Side-Strommessung

Frage: Ist die Platzierung eines 100-Ω-Widerstands vor einem MOSFET-Gate Voraussetzung für Stabilität?

Antwort:

Fragen Sie einen erfahrenen Ingenieur — zum Beispiel Gureux, der Professor in der folgenden Story, — wie man ein MOSFET-Gate beschaltet und Sie werden vielleicht hören „mit einem Widerstand, mit etwa 100 Ω”. Trotz dieser Sicherheit wundert man sich warum und stellt den Nutzen sowie den Widerstandswert in Frage. Aus reiner Neugier werden wir diese Frage anhand des folgenden Beispiels untersuchen.

Neubean, ein junger Applikationsingenieur, möchte herausfinden, ob es tatsächlich notwendig ist, aus Gründen der Stabilisierung ein MOSFET-Gate mit einem 100-Ω-Widerstand zu beschalten. Gureux, ein Applikationsingenieur mit 30 Jahren Erfahrung, überwacht die Experimente und gibt fachliche Ratschläge.

Die High-Side-Strommessung

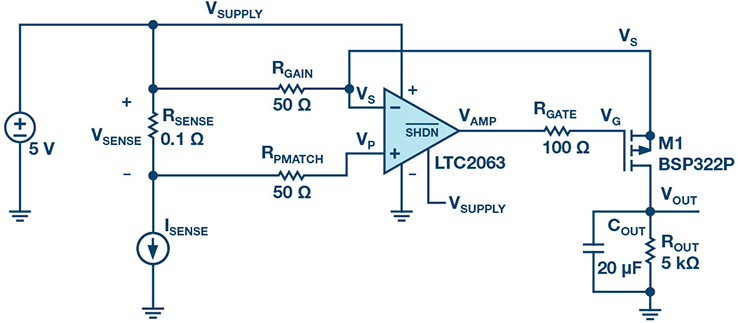

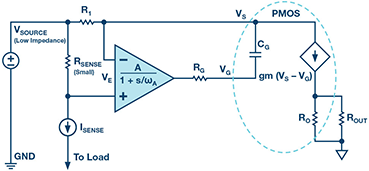

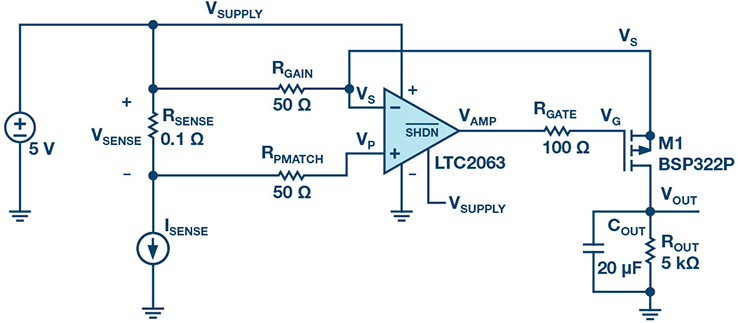

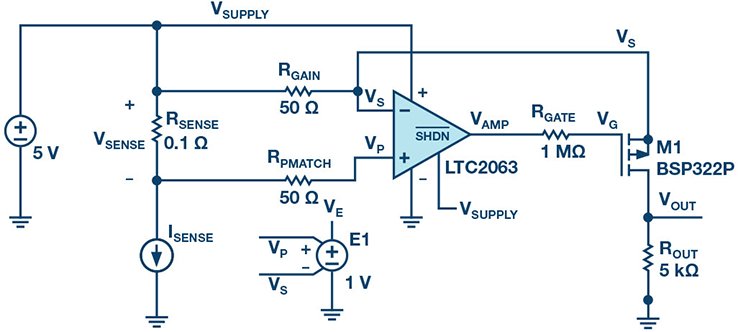

Bild 1. High-Side-Strommessung.

Die Schaltung in Bild 1 zeigt ein typisches Beispiel für eine High-Side-Strommessung. Negatives Feedback versucht, die Spannung VSENSE auf einen Verstärkungswiderstand RGAIN zu zwingen. Der Strom durch RGAIN fließt über den P-Kanal-MOSFET (PMOS) zum Widerstand ROUT, an dem eine auf Masse bezogene Ausgangsspannung entsteht. Die gesamte Verstärkung beträgt

Bild 1. High-Side-Strommessung.

Die Schaltung in Bild 1 zeigt ein typisches Beispiel für eine High-Side-Strommessung. Negatives Feedback versucht, die Spannung VSENSE auf einen Verstärkungswiderstand RGAIN zu zwingen. Der Strom durch RGAIN fließt über den P-Kanal-MOSFET (PMOS) zum Widerstand ROUT, an dem eine auf Masse bezogene Ausgangsspannung entsteht. Die gesamte Verstärkung beträgt

Ein optionaler Kondensator COUT über dem Widerstand ROUT dient zum Filtern der Ausgangsspannung. Selbst wenn der Drain-Strom des PMOS schnell dem gemessenen Strom folgt, wird die Ausgangsspannung einen exponentiellen Verlauf erster Ordnung zeigen.

Der Widerstand RGATE im Schaltbild trennt den Verstärker vom PMOS-Gate. Was ist der Wert? “100 Ω natürlich!”, könnte der erfahrene Kollege Gureux sagen.

Hohe Widerstandswerte ausprobieren

Unser Freund Neubean, ein Student von Gureux, denkt über diesen Gate-Widerstand nach. Neubean denkt, dass er mit genügend Kapazität zwischen Gate und Source oder mit einem genügend großen Gate-Widerstand Stabilitätsprobleme hervorrufen könnte. Sobald klar ist, dass RGATE und CGATE nachteilig zusammenwirken, wird es möglich sein, den Mythos, dass 100 Ω oder praktisch jeder Gate-Widerstand automatisch geeignet sind, zu widerlegen.

Ein optionaler Kondensator COUT über dem Widerstand ROUT dient zum Filtern der Ausgangsspannung. Selbst wenn der Drain-Strom des PMOS schnell dem gemessenen Strom folgt, wird die Ausgangsspannung einen exponentiellen Verlauf erster Ordnung zeigen.

Der Widerstand RGATE im Schaltbild trennt den Verstärker vom PMOS-Gate. Was ist der Wert? “100 Ω natürlich!”, könnte der erfahrene Kollege Gureux sagen.

Hohe Widerstandswerte ausprobieren

Unser Freund Neubean, ein Student von Gureux, denkt über diesen Gate-Widerstand nach. Neubean denkt, dass er mit genügend Kapazität zwischen Gate und Source oder mit einem genügend großen Gate-Widerstand Stabilitätsprobleme hervorrufen könnte. Sobald klar ist, dass RGATE und CGATE nachteilig zusammenwirken, wird es möglich sein, den Mythos, dass 100 Ω oder praktisch jeder Gate-Widerstand automatisch geeignet sind, zu widerlegen.

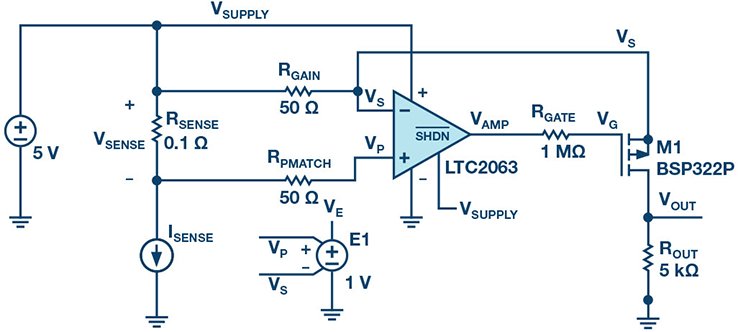

Bild 2. High-Side-Strommesssimulation.

Bild 2 zeigt ein Beispiel einer LTspice-Simulation zur Verdeutlichung des Schaltungsverhaltens. Neubean führt Simulationen durch, um die Stabilitätsprobleme zu zeigen, von denen er glaubt, dass sie mit zunehmendem RGATE auftreten. Letzten Endes sollte die Polstelle von RGATE und CGATE den zur offenen Regelschleife gehörenden Phasenspielraum nachteilig beeinträchtigen. Dennoch, zu Neubeans Verwunderung, ergibt sich bei keinem Wert von RGATE irgendeine Art von Problem beim Verhalten im Zeitbereich.

Es stellt sich heraus – die Schaltung ist nicht einfach

Bild 2. High-Side-Strommesssimulation.

Bild 2 zeigt ein Beispiel einer LTspice-Simulation zur Verdeutlichung des Schaltungsverhaltens. Neubean führt Simulationen durch, um die Stabilitätsprobleme zu zeigen, von denen er glaubt, dass sie mit zunehmendem RGATE auftreten. Letzten Endes sollte die Polstelle von RGATE und CGATE den zur offenen Regelschleife gehörenden Phasenspielraum nachteilig beeinträchtigen. Dennoch, zu Neubeans Verwunderung, ergibt sich bei keinem Wert von RGATE irgendeine Art von Problem beim Verhalten im Zeitbereich.

Es stellt sich heraus – die Schaltung ist nicht einfach

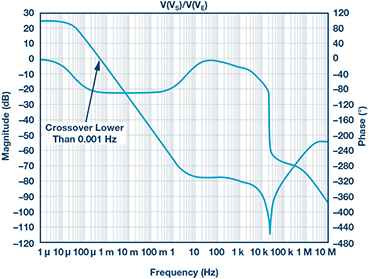

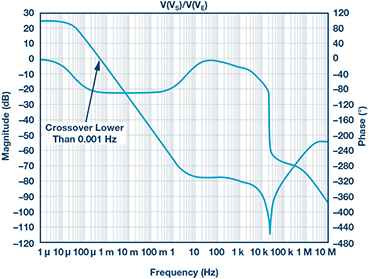

Bild 3. Frequenzverlauf von der Fehler- zur Quell-Spannung.

Bei der Untersuchung des Frequenzverlaufs stellt Neubean fest, dass er das Verhalten des offenen Regelkreises ermitteln muss. Der Vorwärtspfad, der die Regelschleife in Kombination mit der Gegenkopplung bei Verstärkung Eins (Unity Negative Feedback) bildet, beginnt bei der Differenz und endet am resultierenden negativen Eingang. Anschließend simuliert Neubean und plottet VS/(VP – VS) oder VS/VE. Bild 3 zeigt den Frequenzverlauf für dieses Verhalten bei offener Regelschleife. Das Bode-Diagramm von Bild 3 zeigt eine nur sehr niedrige DC-Verstärkung und keine Anzeichen von Problemen bezüglich des Phasenspielraums beim Übergang. Genau genommen sieht der Plot insgesamt merkwürdig aus, da die Übergangsfrequenz weniger als 0,001 Hz beträgt.

Bild 3. Frequenzverlauf von der Fehler- zur Quell-Spannung.

Bei der Untersuchung des Frequenzverlaufs stellt Neubean fest, dass er das Verhalten des offenen Regelkreises ermitteln muss. Der Vorwärtspfad, der die Regelschleife in Kombination mit der Gegenkopplung bei Verstärkung Eins (Unity Negative Feedback) bildet, beginnt bei der Differenz und endet am resultierenden negativen Eingang. Anschließend simuliert Neubean und plottet VS/(VP – VS) oder VS/VE. Bild 3 zeigt den Frequenzverlauf für dieses Verhalten bei offener Regelschleife. Das Bode-Diagramm von Bild 3 zeigt eine nur sehr niedrige DC-Verstärkung und keine Anzeichen von Problemen bezüglich des Phasenspielraums beim Übergang. Genau genommen sieht der Plot insgesamt merkwürdig aus, da die Übergangsfrequenz weniger als 0,001 Hz beträgt.

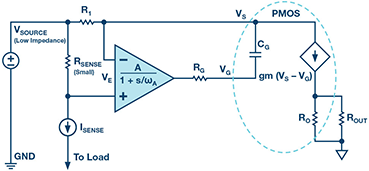

Bild 4. High-Side-Messchaltung als Blockdiagramm.

Die Zerlegung der Schaltung in ein Steuersystem zeigt Bild 4. Der LTC2063, genau wie fast alle OPVs mit Spannungsrückkopplung, startet mit hoher DC-Verstärkung und einer Polstelle. Der OPV verstärkt das Fehlersignal und treibt das PMOS-Gate durch den RGATE–CGATE-Filter. CGATE und die PMOS-Source sind zusammen mit dem –IN-Eingang des OPV verbunden. RGAIN ist von diesem Schaltungsknoten aus mit der Source mit niedriger Impedanz verbunden. Selbst in Bild 4 könnte man annehmen, dass der RGATE–CGATE-Filter Stabilitätsprobleme verursacht, speziell wenn RGATE wesentlich größer ist als RGAIN. Letzten Endes treten bei der CGATE-Spannung, die direkt den Strom RGAIN im System beeinträchtigt, keine Änderungen am OPV-Ausgang auf.

Neubean bietet eine Erklärung dafür an, warum vielleicht RGATE und CGATE keine Instabilität hervorrufen: “Nun, die Gate-Source-Spannung ist fest und somit ist der RGATE–CGATE-Schaltkreis nicht relevant. Man muss lediglich das Gate einstellen und die Source folgt.“ Es ist ein Source-Folger.”

Sein erfahrenerer Kollege Gureux sagt: “Eigentlich nicht. Dies gilt nur, wenn der PMOS normal als Verstärkerblock in der Schaltung arbeitet.”

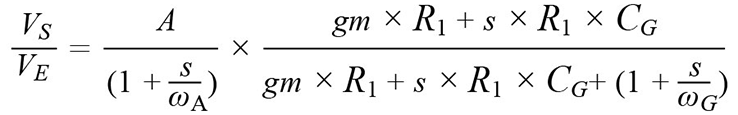

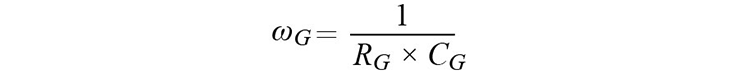

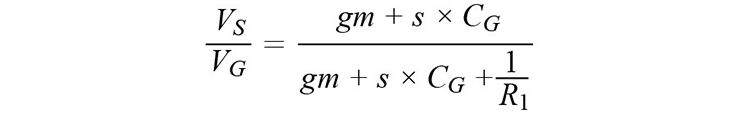

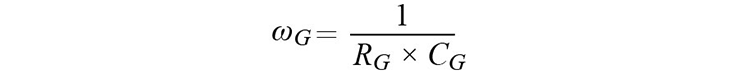

Dadurch angespornt, befasst sich Neubean mit dem mathematischen Zusammenhang. Was wäre, wenn man das Verhalten zwischen Source und Gate des PMOS direkt modellieren könnte? Mit anderen Worten, was ist V(VS)/V(VG)? Neubean geht zur Tafel und schreibt die folgenden Gleichungen an:

Bild 4. High-Side-Messchaltung als Blockdiagramm.

Die Zerlegung der Schaltung in ein Steuersystem zeigt Bild 4. Der LTC2063, genau wie fast alle OPVs mit Spannungsrückkopplung, startet mit hoher DC-Verstärkung und einer Polstelle. Der OPV verstärkt das Fehlersignal und treibt das PMOS-Gate durch den RGATE–CGATE-Filter. CGATE und die PMOS-Source sind zusammen mit dem –IN-Eingang des OPV verbunden. RGAIN ist von diesem Schaltungsknoten aus mit der Source mit niedriger Impedanz verbunden. Selbst in Bild 4 könnte man annehmen, dass der RGATE–CGATE-Filter Stabilitätsprobleme verursacht, speziell wenn RGATE wesentlich größer ist als RGAIN. Letzten Endes treten bei der CGATE-Spannung, die direkt den Strom RGAIN im System beeinträchtigt, keine Änderungen am OPV-Ausgang auf.

Neubean bietet eine Erklärung dafür an, warum vielleicht RGATE und CGATE keine Instabilität hervorrufen: “Nun, die Gate-Source-Spannung ist fest und somit ist der RGATE–CGATE-Schaltkreis nicht relevant. Man muss lediglich das Gate einstellen und die Source folgt.“ Es ist ein Source-Folger.”

Sein erfahrenerer Kollege Gureux sagt: “Eigentlich nicht. Dies gilt nur, wenn der PMOS normal als Verstärkerblock in der Schaltung arbeitet.”

Dadurch angespornt, befasst sich Neubean mit dem mathematischen Zusammenhang. Was wäre, wenn man das Verhalten zwischen Source und Gate des PMOS direkt modellieren könnte? Mit anderen Worten, was ist V(VS)/V(VG)? Neubean geht zur Tafel und schreibt die folgenden Gleichungen an:

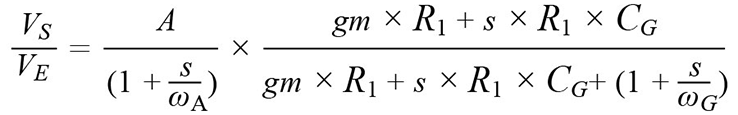

mit

mit

OPV-Verstärkung A und OPV-Pol ωA.

OPV-Verstärkung A und OPV-Pol ωA.

Neubean erkennt sofort den wichtigen Term gm. Was ist gm? Für einen MOSFET gilt

Neubean erkennt sofort den wichtigen Term gm. Was ist gm? Für einen MOSFET gilt

Bei einem Blick auf die Schaltung in Bild 1 geht Neubean ein Licht auf. Bei einem Strom von Null Ampere durch den Widerstand RSENSE sollte der Strom durch den PMOS ebenfalls Null Ampere betragen. Bei einem Strom von Null Ampere ist gm Null, da der PMOS effektiv ausgeschaltet ist, nicht genutzt wird und nicht vorgespannt ist und keine Verstärkung hat. Wenn gm = 0 ist VS/VE 0 bei 0 Hz und VS/VG 0 bei 0 Hz. Somit ist keine Verstärkung vorhanden und die Plots in Bild 3 können letztendlich gültig sein.

Instabilitäten mit dem LTC2063 versuchen

Gerüstet mit dieser Erkenntnis, probiert Neubean schnell ein paar Simulationen mit einem Strom ISENSE, der nicht gleich Null ist.

Bei einem Blick auf die Schaltung in Bild 1 geht Neubean ein Licht auf. Bei einem Strom von Null Ampere durch den Widerstand RSENSE sollte der Strom durch den PMOS ebenfalls Null Ampere betragen. Bei einem Strom von Null Ampere ist gm Null, da der PMOS effektiv ausgeschaltet ist, nicht genutzt wird und nicht vorgespannt ist und keine Verstärkung hat. Wenn gm = 0 ist VS/VE 0 bei 0 Hz und VS/VG 0 bei 0 Hz. Somit ist keine Verstärkung vorhanden und die Plots in Bild 3 können letztendlich gültig sein.

Instabilitäten mit dem LTC2063 versuchen

Gerüstet mit dieser Erkenntnis, probiert Neubean schnell ein paar Simulationen mit einem Strom ISENSE, der nicht gleich Null ist.

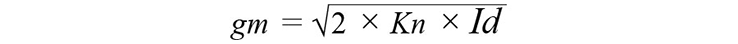

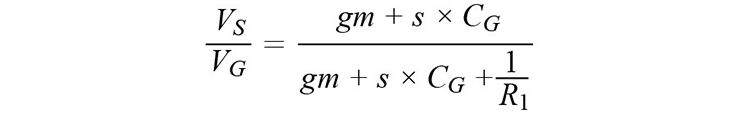

Bild 5. Frequenzverlauf von der Fehlerspannung zur Quell-Spannung bei einem Messstrom von ungleich Null.

Bild 5 zeigt, was wie ein wesentlich normalerer Verstärkungs/Phasen-Plot des Verlaufs von VE zu VS bei einem Übergang von >0 dB zu <0 dB aussieht. Bild 5 sollte etwa 2 kHz zeigen, mit reichlich PM bei 100 Ω, etwas weniger PM bei 100 kΩ und noch weniger mit 1 MΩ, aber nicht instabil.

Neubean geht ins Labor und wählt einen Messstrom mit dem High-Side-Messschaltkreis LTC2063. Er fügt einen RGATE mit hohem Widerstandswert ein, zuerst 100 kΩ und dann 1 MΩ, und erwartet ein instabiles Verhalten, zumindest aber eine Art Ringing. Doch leider ist das nicht der Fall.

Er versucht, den Drain-Strom im MOSFET zu erhöhen, indem er zuerst einen höheren ISENSE wählt, und dann einen kleineren Verstärkungswiderstand RGAIN. Nichts kann die Schaltung destabilisieren.

Bild 5. Frequenzverlauf von der Fehlerspannung zur Quell-Spannung bei einem Messstrom von ungleich Null.

Bild 5 zeigt, was wie ein wesentlich normalerer Verstärkungs/Phasen-Plot des Verlaufs von VE zu VS bei einem Übergang von >0 dB zu <0 dB aussieht. Bild 5 sollte etwa 2 kHz zeigen, mit reichlich PM bei 100 Ω, etwas weniger PM bei 100 kΩ und noch weniger mit 1 MΩ, aber nicht instabil.

Neubean geht ins Labor und wählt einen Messstrom mit dem High-Side-Messschaltkreis LTC2063. Er fügt einen RGATE mit hohem Widerstandswert ein, zuerst 100 kΩ und dann 1 MΩ, und erwartet ein instabiles Verhalten, zumindest aber eine Art Ringing. Doch leider ist das nicht der Fall.

Er versucht, den Drain-Strom im MOSFET zu erhöhen, indem er zuerst einen höheren ISENSE wählt, und dann einen kleineren Verstärkungswiderstand RGAIN. Nichts kann die Schaltung destabilisieren.

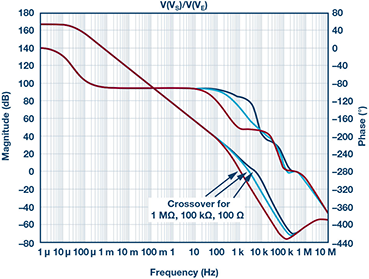

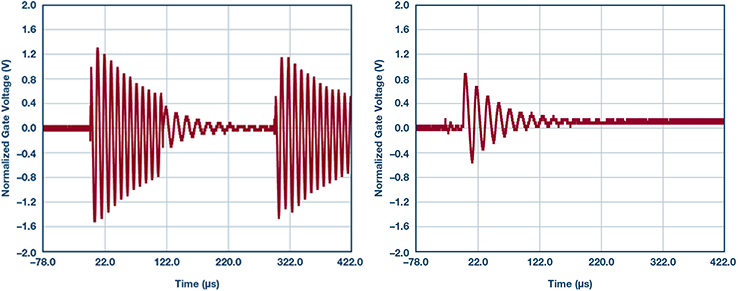

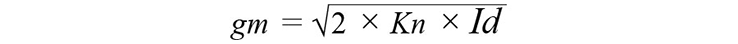

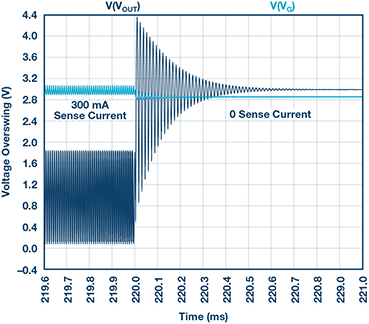

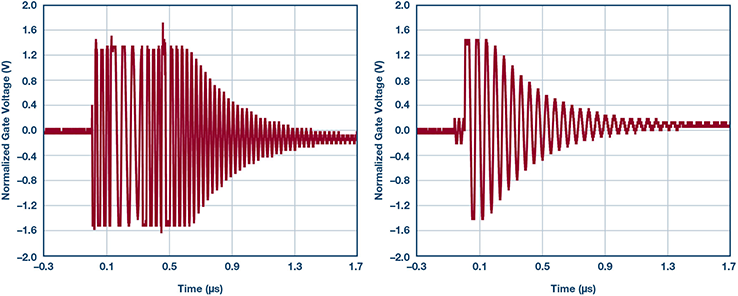

Bild 6. Zeitbereichsplot mit Schwingungen.

Er wendet sich erneut der Simulation zu und versucht, eine Phasenreserve mit einem Strom von ISENSE, der nicht Null ist, zu verringern. Selbst in der Simulation erscheint es schwierig, falls nicht unmöglich, Instabilität oder geringe Phasenreserve zu finden.

Neubean fragt Gureux, warum es ihm nicht gelingt, den Schaltkreis zu destabilisieren. Gureux rät ihm, sich die Zahlen genauer zu betrachten. Neubean ist Rätsel von Gureux gewohnt und untersucht, was die tatsächliche Polstelle in Verbindung mit RGATE und die gesamte Gate-Kapazität sein könnte. Bei 100 Ω und 250 pF liegt die Polstelle bei 6,4 MHz; mit 100 kΩ bei 6,4 kHz und mit 1 MΩ bei 640 Hz. Das Verstärkungs-Bandbreiten-Produkt (GBP) des LTC2063 beträgt 20 kHz. Wenn der LTC2063 mit Verstärkung betrieben wird, kann die Crossover-Frequenz bei geschlossenem Regelkreis leicht unter den Bereich des RGATE–CGATE-Pols gleiten.

Ja, Instabilität ist erreichbar

Bild 6. Zeitbereichsplot mit Schwingungen.

Er wendet sich erneut der Simulation zu und versucht, eine Phasenreserve mit einem Strom von ISENSE, der nicht Null ist, zu verringern. Selbst in der Simulation erscheint es schwierig, falls nicht unmöglich, Instabilität oder geringe Phasenreserve zu finden.

Neubean fragt Gureux, warum es ihm nicht gelingt, den Schaltkreis zu destabilisieren. Gureux rät ihm, sich die Zahlen genauer zu betrachten. Neubean ist Rätsel von Gureux gewohnt und untersucht, was die tatsächliche Polstelle in Verbindung mit RGATE und die gesamte Gate-Kapazität sein könnte. Bei 100 Ω und 250 pF liegt die Polstelle bei 6,4 MHz; mit 100 kΩ bei 6,4 kHz und mit 1 MΩ bei 640 Hz. Das Verstärkungs-Bandbreiten-Produkt (GBP) des LTC2063 beträgt 20 kHz. Wenn der LTC2063 mit Verstärkung betrieben wird, kann die Crossover-Frequenz bei geschlossenem Regelkreis leicht unter den Bereich des RGATE–CGATE-Pols gleiten.

Ja, Instabilität ist erreichbar

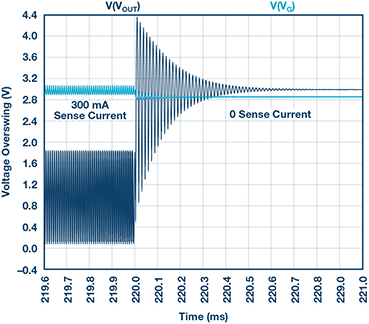

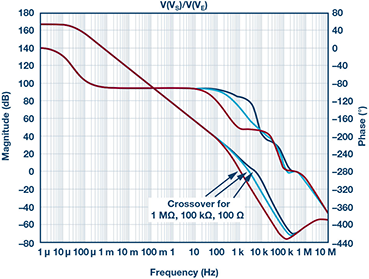

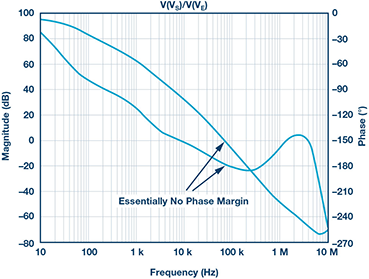

Bild 7. Normales Bodediagramm sobald man Strom zugibt, VE zu VS, mit schrecklicher Phasenreserve.

Indem er erkennt, dass das dynamische Verhalten des OPV sich bis in den Bereich des RGATE – CGATE Pols fortsetzen muss, wählt Neubean ein größeres GBP. Der 5-V-OPV LTC6255 passt direkt in die Schaltung mit einem höheren GBP von 6,5 MHz.

Eifrig versucht Neubean eine Simulation mit Strom, dem LTC6255, 100 kΩ Gate-Widerstand, und mit 300 mA Messstrom. Neubean macht dann weiter und bringt RGATE in die Simulation ein. Mit genügend RGATE kann eine zusätzliche Polstelle einen Schaltkreis destabilisieren.

Bild 6 und Bild 7 zeigt Simulationsergebnisse mit hohen RGATE-Werten. Bei einem konstanten Messstrom von 300 mA zeigt die Simulation Instabilität.

Laborergebnisse

Weil er sehen möchte, ob der Schaltkreis sich beim Messen eines Stromes von ungleich Null negativ verhalten könnte, probiert Neubean den LTC6255 mit einem stufenförmigen verlaufenden Laststrom und nutzt drei verschiedene RGATE-Werte. ISENSE geht von einer Basis von 60 mA auf einen höheren Wert von 220 mA über, ermöglicht durch einen Schalter, der mehr parallelen Lastwiderstand einbringt. Es gibt keine Nullstrom ISENSE-Messung, da bereits gezeigt wurde, dass die MOSFET-Verstärkung in diesem Fall zu niedrig ist.

In der Tat zeigt Bild 8 schließlich eine beeinträchtigte Stabilität mit Widerständen von 100 kΩ und 1 MΩ. Da die Ausgangsspannung stark gefiltert ist, wird die Gate-Spannung zum Detektor für Ringing. Ringing kennzeichnet eine geringe oder negative Phasenreserve und die Ringing-Frequenz bezeichnet die Übergangsfrequenz (Crossover Frequency).

Bild 7. Normales Bodediagramm sobald man Strom zugibt, VE zu VS, mit schrecklicher Phasenreserve.

Indem er erkennt, dass das dynamische Verhalten des OPV sich bis in den Bereich des RGATE – CGATE Pols fortsetzen muss, wählt Neubean ein größeres GBP. Der 5-V-OPV LTC6255 passt direkt in die Schaltung mit einem höheren GBP von 6,5 MHz.

Eifrig versucht Neubean eine Simulation mit Strom, dem LTC6255, 100 kΩ Gate-Widerstand, und mit 300 mA Messstrom. Neubean macht dann weiter und bringt RGATE in die Simulation ein. Mit genügend RGATE kann eine zusätzliche Polstelle einen Schaltkreis destabilisieren.

Bild 6 und Bild 7 zeigt Simulationsergebnisse mit hohen RGATE-Werten. Bei einem konstanten Messstrom von 300 mA zeigt die Simulation Instabilität.

Laborergebnisse

Weil er sehen möchte, ob der Schaltkreis sich beim Messen eines Stromes von ungleich Null negativ verhalten könnte, probiert Neubean den LTC6255 mit einem stufenförmigen verlaufenden Laststrom und nutzt drei verschiedene RGATE-Werte. ISENSE geht von einer Basis von 60 mA auf einen höheren Wert von 220 mA über, ermöglicht durch einen Schalter, der mehr parallelen Lastwiderstand einbringt. Es gibt keine Nullstrom ISENSE-Messung, da bereits gezeigt wurde, dass die MOSFET-Verstärkung in diesem Fall zu niedrig ist.

In der Tat zeigt Bild 8 schließlich eine beeinträchtigte Stabilität mit Widerständen von 100 kΩ und 1 MΩ. Da die Ausgangsspannung stark gefiltert ist, wird die Gate-Spannung zum Detektor für Ringing. Ringing kennzeichnet eine geringe oder negative Phasenreserve und die Ringing-Frequenz bezeichnet die Übergangsfrequenz (Crossover Frequency).

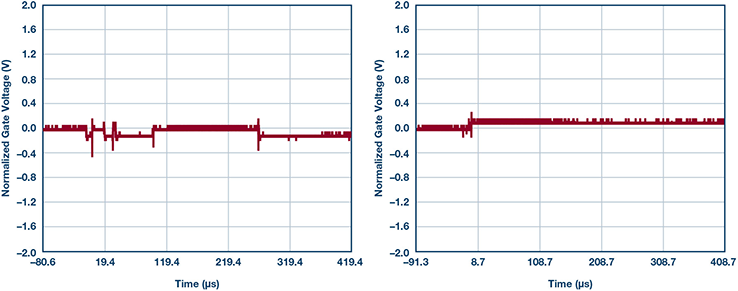

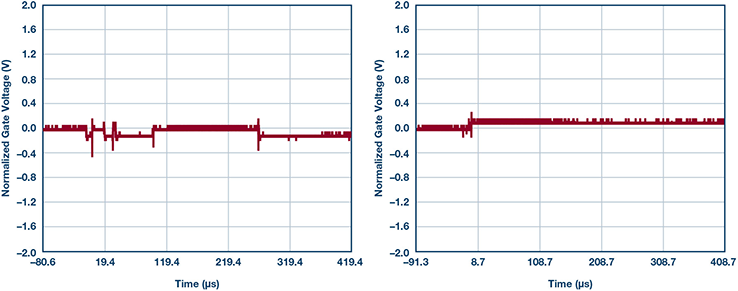

Bild 8. RGATE = 100 Ω, Strom von niedriger zu hoher Transiente. / Bild 9. RGATE = 100 Ω, Strom von hoher zu niedriger Transiente.

Bild 8. RGATE = 100 Ω, Strom von niedriger zu hoher Transiente. / Bild 9. RGATE = 100 Ω, Strom von hoher zu niedriger Transiente.

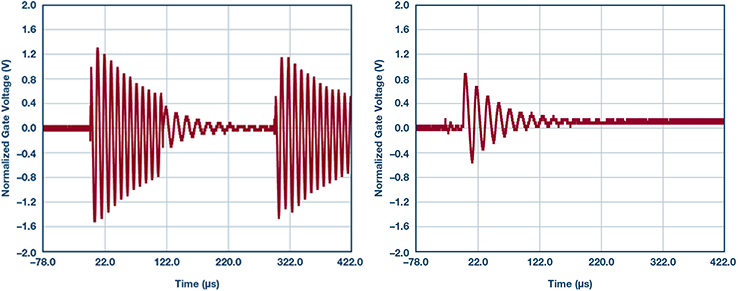

Bild 10. RGATE = 100 kΩ, Strom von niedriger zu hoher Transiente. / Bild 11. RGATE = 100 kΩ, Strom von hoher zu niedriger Transiente.

Bild 10. RGATE = 100 kΩ, Strom von niedriger zu hoher Transiente. / Bild 11. RGATE = 100 kΩ, Strom von hoher zu niedriger Transiente.

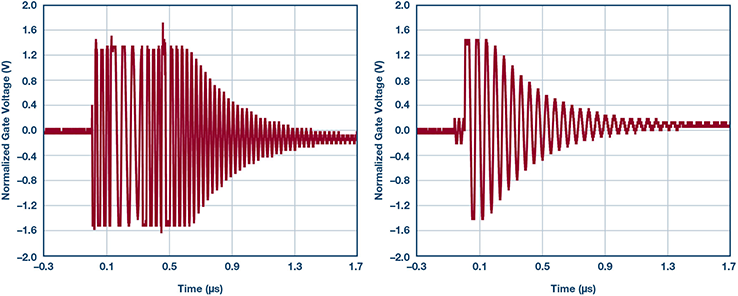

Bild 12. RGATE = 1 MΩ, Strom von niedriger zu hoher Transiente. / Bild 13. RGATE = 1 MΩ, Strom von hoher zu niedriger Transiente.

Ein Augenblick der Ideenfindung

Neubean wird sich bewusst, dass er viele High-Side-Messschaltkreis-ICs gesehen hat und es unglücklicherweise keine Chance für einen Ingenieur gibt, den Gate-Widerstand zu bestimmen, da sich alle Funktionen innerhalb des Bausteins befinden. Beispiele, die ihm in den Sinn kamen, waren die Hochvolt-/High-Side-Strommessbausteine AD8212, LTC6101, LTC6102 und LTC6104. Tatsächlich nutzt der AD8212 einen PNP-Transistor statt einen PMOS-FET. Er sagt Gureux, “Hey, es ist wirklich nicht wichtig, da moderne Bausteine dieses Problem bereits lösen.”

Als ob er diese Bemerkung erwartet hätte, und Neubean fast das Wort abschneidend, antwortet der Professor: “Angenommen du möchtest eine Kombination aus extrem niedrigem Versorgungsstrom und einen driftfreien Eingangsoffset, wie etwa in einem batteriegespeisten Messinstrument. Und du möchtest vielleicht einen LTC2063 oder LTC2066 als primären Verstärker einsetzen. Oder, vielleicht musst du einen niedrigen Strom messen, möglicherweise über einen Shunt mit 470 Ω und so genau und rauscharm wie möglich; in diesem Fall könntest du den ADA4528 einsetzen, der Rail-to-Rail-Eingangsverhalten hat. In diesen Fällen musst du dich mit der MOSFET-Treiberschaltung befassen.”

Und so…

Offensichtlich ist es dann möglich, die High-Side-Strommmessschaltung mit einem zu großen Gate-Widerstand zu destabilisieren. Neubean führt dieses Ergebnis auf seinen wohlwollenden Lehrer Gureux zurück. Gureux stellt fest, dass RGATE in der Tat die Schaltung destabilisieren kann, doch die anfängliche Unfähigkeit, dieses Verhalten herauszufinden, resultierte aus einem falsch formulierten Problem. Es muss Verstärkung vorhanden sein, was in dieser Schaltung erforderlich ist, um ein Non-Zero-Signal zu messen.

Gureux antwortet: “Sicher, wenn ein Pol die Phasenreserve bei einem Übergang (Crossover) negativ beeinträchtigt, entsteht Ringing. Doch dein hinzugefügter Gate-Widerstand von 1 MΩ ist absurd — selbst 100 kΩ ist verrückt. Denke daran, es ist immer gut zu versuchen, den Ausgangsstrom eines OPV zu begrenzen, falls er versucht, eine Gate-Kapazität von einer zur anderen Versorgungsschiene zum Schwingen zu bringen.

Neubean stimmt zu. “Welchen Widerstandswert verwende ich also?” Gureux bemerkt zuversichtlich: “100 Ω”.

Bild 12. RGATE = 1 MΩ, Strom von niedriger zu hoher Transiente. / Bild 13. RGATE = 1 MΩ, Strom von hoher zu niedriger Transiente.

Ein Augenblick der Ideenfindung

Neubean wird sich bewusst, dass er viele High-Side-Messschaltkreis-ICs gesehen hat und es unglücklicherweise keine Chance für einen Ingenieur gibt, den Gate-Widerstand zu bestimmen, da sich alle Funktionen innerhalb des Bausteins befinden. Beispiele, die ihm in den Sinn kamen, waren die Hochvolt-/High-Side-Strommessbausteine AD8212, LTC6101, LTC6102 und LTC6104. Tatsächlich nutzt der AD8212 einen PNP-Transistor statt einen PMOS-FET. Er sagt Gureux, “Hey, es ist wirklich nicht wichtig, da moderne Bausteine dieses Problem bereits lösen.”

Als ob er diese Bemerkung erwartet hätte, und Neubean fast das Wort abschneidend, antwortet der Professor: “Angenommen du möchtest eine Kombination aus extrem niedrigem Versorgungsstrom und einen driftfreien Eingangsoffset, wie etwa in einem batteriegespeisten Messinstrument. Und du möchtest vielleicht einen LTC2063 oder LTC2066 als primären Verstärker einsetzen. Oder, vielleicht musst du einen niedrigen Strom messen, möglicherweise über einen Shunt mit 470 Ω und so genau und rauscharm wie möglich; in diesem Fall könntest du den ADA4528 einsetzen, der Rail-to-Rail-Eingangsverhalten hat. In diesen Fällen musst du dich mit der MOSFET-Treiberschaltung befassen.”

Und so…

Offensichtlich ist es dann möglich, die High-Side-Strommmessschaltung mit einem zu großen Gate-Widerstand zu destabilisieren. Neubean führt dieses Ergebnis auf seinen wohlwollenden Lehrer Gureux zurück. Gureux stellt fest, dass RGATE in der Tat die Schaltung destabilisieren kann, doch die anfängliche Unfähigkeit, dieses Verhalten herauszufinden, resultierte aus einem falsch formulierten Problem. Es muss Verstärkung vorhanden sein, was in dieser Schaltung erforderlich ist, um ein Non-Zero-Signal zu messen.

Gureux antwortet: “Sicher, wenn ein Pol die Phasenreserve bei einem Übergang (Crossover) negativ beeinträchtigt, entsteht Ringing. Doch dein hinzugefügter Gate-Widerstand von 1 MΩ ist absurd — selbst 100 kΩ ist verrückt. Denke daran, es ist immer gut zu versuchen, den Ausgangsstrom eines OPV zu begrenzen, falls er versucht, eine Gate-Kapazität von einer zur anderen Versorgungsschiene zum Schwingen zu bringen.

Neubean stimmt zu. “Welchen Widerstandswert verwende ich also?” Gureux bemerkt zuversichtlich: “100 Ω”.

Autorenvorstellung: Aaron Schultz [aaron.schultz@analog.com] ist Applikationsingenieur-Manager in der LPS Business Unit bei © Analog Devices. Seine verschiedenen System-Engineering-Funktionen im Design und im Applikationsbereich brachten ihn mit unterschiedlichen Schwerpunkten zusammen. Angefangen bei Batteriemanagement, Photovoltaik, dimmbare LED-Treiberschaltungen, Niedervolt- und Hochstrom-DC/DC-Wandlung, High-Speed Glasfaserkommunikation, R&D für fortschrittliches DDR3 Memory, Kundentoolentwicklung, Validierung und Basis-Analogschaltkreise, während er über die Hälfte seiner beruflichen Laufbahn im Bereich Leistungswandlung zubrachte. Er hat 1993 sein Studium an der Carnegie Mellon University abgeschlossen und MIT im Jahr 1995.

Bild 1. High-Side-Strommessung.

Die Schaltung in Bild 1 zeigt ein typisches Beispiel für eine High-Side-Strommessung. Negatives Feedback versucht, die Spannung VSENSE auf einen Verstärkungswiderstand RGAIN zu zwingen. Der Strom durch RGAIN fließt über den P-Kanal-MOSFET (PMOS) zum Widerstand ROUT, an dem eine auf Masse bezogene Ausgangsspannung entsteht. Die gesamte Verstärkung beträgt

Bild 1. High-Side-Strommessung.

Die Schaltung in Bild 1 zeigt ein typisches Beispiel für eine High-Side-Strommessung. Negatives Feedback versucht, die Spannung VSENSE auf einen Verstärkungswiderstand RGAIN zu zwingen. Der Strom durch RGAIN fließt über den P-Kanal-MOSFET (PMOS) zum Widerstand ROUT, an dem eine auf Masse bezogene Ausgangsspannung entsteht. Die gesamte Verstärkung beträgt

Ein optionaler Kondensator COUT über dem Widerstand ROUT dient zum Filtern der Ausgangsspannung. Selbst wenn der Drain-Strom des PMOS schnell dem gemessenen Strom folgt, wird die Ausgangsspannung einen exponentiellen Verlauf erster Ordnung zeigen.

Der Widerstand RGATE im Schaltbild trennt den Verstärker vom PMOS-Gate. Was ist der Wert? “100 Ω natürlich!”, könnte der erfahrene Kollege Gureux sagen.

Hohe Widerstandswerte ausprobieren

Unser Freund Neubean, ein Student von Gureux, denkt über diesen Gate-Widerstand nach. Neubean denkt, dass er mit genügend Kapazität zwischen Gate und Source oder mit einem genügend großen Gate-Widerstand Stabilitätsprobleme hervorrufen könnte. Sobald klar ist, dass RGATE und CGATE nachteilig zusammenwirken, wird es möglich sein, den Mythos, dass 100 Ω oder praktisch jeder Gate-Widerstand automatisch geeignet sind, zu widerlegen.

Ein optionaler Kondensator COUT über dem Widerstand ROUT dient zum Filtern der Ausgangsspannung. Selbst wenn der Drain-Strom des PMOS schnell dem gemessenen Strom folgt, wird die Ausgangsspannung einen exponentiellen Verlauf erster Ordnung zeigen.

Der Widerstand RGATE im Schaltbild trennt den Verstärker vom PMOS-Gate. Was ist der Wert? “100 Ω natürlich!”, könnte der erfahrene Kollege Gureux sagen.

Hohe Widerstandswerte ausprobieren

Unser Freund Neubean, ein Student von Gureux, denkt über diesen Gate-Widerstand nach. Neubean denkt, dass er mit genügend Kapazität zwischen Gate und Source oder mit einem genügend großen Gate-Widerstand Stabilitätsprobleme hervorrufen könnte. Sobald klar ist, dass RGATE und CGATE nachteilig zusammenwirken, wird es möglich sein, den Mythos, dass 100 Ω oder praktisch jeder Gate-Widerstand automatisch geeignet sind, zu widerlegen.

Bild 2. High-Side-Strommesssimulation.

Bild 2 zeigt ein Beispiel einer LTspice-Simulation zur Verdeutlichung des Schaltungsverhaltens. Neubean führt Simulationen durch, um die Stabilitätsprobleme zu zeigen, von denen er glaubt, dass sie mit zunehmendem RGATE auftreten. Letzten Endes sollte die Polstelle von RGATE und CGATE den zur offenen Regelschleife gehörenden Phasenspielraum nachteilig beeinträchtigen. Dennoch, zu Neubeans Verwunderung, ergibt sich bei keinem Wert von RGATE irgendeine Art von Problem beim Verhalten im Zeitbereich.

Es stellt sich heraus – die Schaltung ist nicht einfach

Bild 2. High-Side-Strommesssimulation.

Bild 2 zeigt ein Beispiel einer LTspice-Simulation zur Verdeutlichung des Schaltungsverhaltens. Neubean führt Simulationen durch, um die Stabilitätsprobleme zu zeigen, von denen er glaubt, dass sie mit zunehmendem RGATE auftreten. Letzten Endes sollte die Polstelle von RGATE und CGATE den zur offenen Regelschleife gehörenden Phasenspielraum nachteilig beeinträchtigen. Dennoch, zu Neubeans Verwunderung, ergibt sich bei keinem Wert von RGATE irgendeine Art von Problem beim Verhalten im Zeitbereich.

Es stellt sich heraus – die Schaltung ist nicht einfach

Bild 3. Frequenzverlauf von der Fehler- zur Quell-Spannung.

Bei der Untersuchung des Frequenzverlaufs stellt Neubean fest, dass er das Verhalten des offenen Regelkreises ermitteln muss. Der Vorwärtspfad, der die Regelschleife in Kombination mit der Gegenkopplung bei Verstärkung Eins (Unity Negative Feedback) bildet, beginnt bei der Differenz und endet am resultierenden negativen Eingang. Anschließend simuliert Neubean und plottet VS/(VP – VS) oder VS/VE. Bild 3 zeigt den Frequenzverlauf für dieses Verhalten bei offener Regelschleife. Das Bode-Diagramm von Bild 3 zeigt eine nur sehr niedrige DC-Verstärkung und keine Anzeichen von Problemen bezüglich des Phasenspielraums beim Übergang. Genau genommen sieht der Plot insgesamt merkwürdig aus, da die Übergangsfrequenz weniger als 0,001 Hz beträgt.

Bild 3. Frequenzverlauf von der Fehler- zur Quell-Spannung.

Bei der Untersuchung des Frequenzverlaufs stellt Neubean fest, dass er das Verhalten des offenen Regelkreises ermitteln muss. Der Vorwärtspfad, der die Regelschleife in Kombination mit der Gegenkopplung bei Verstärkung Eins (Unity Negative Feedback) bildet, beginnt bei der Differenz und endet am resultierenden negativen Eingang. Anschließend simuliert Neubean und plottet VS/(VP – VS) oder VS/VE. Bild 3 zeigt den Frequenzverlauf für dieses Verhalten bei offener Regelschleife. Das Bode-Diagramm von Bild 3 zeigt eine nur sehr niedrige DC-Verstärkung und keine Anzeichen von Problemen bezüglich des Phasenspielraums beim Übergang. Genau genommen sieht der Plot insgesamt merkwürdig aus, da die Übergangsfrequenz weniger als 0,001 Hz beträgt.

Bild 4. High-Side-Messchaltung als Blockdiagramm.

Die Zerlegung der Schaltung in ein Steuersystem zeigt Bild 4. Der LTC2063, genau wie fast alle OPVs mit Spannungsrückkopplung, startet mit hoher DC-Verstärkung und einer Polstelle. Der OPV verstärkt das Fehlersignal und treibt das PMOS-Gate durch den RGATE–CGATE-Filter. CGATE und die PMOS-Source sind zusammen mit dem –IN-Eingang des OPV verbunden. RGAIN ist von diesem Schaltungsknoten aus mit der Source mit niedriger Impedanz verbunden. Selbst in Bild 4 könnte man annehmen, dass der RGATE–CGATE-Filter Stabilitätsprobleme verursacht, speziell wenn RGATE wesentlich größer ist als RGAIN. Letzten Endes treten bei der CGATE-Spannung, die direkt den Strom RGAIN im System beeinträchtigt, keine Änderungen am OPV-Ausgang auf.

Neubean bietet eine Erklärung dafür an, warum vielleicht RGATE und CGATE keine Instabilität hervorrufen: “Nun, die Gate-Source-Spannung ist fest und somit ist der RGATE–CGATE-Schaltkreis nicht relevant. Man muss lediglich das Gate einstellen und die Source folgt.“ Es ist ein Source-Folger.”

Sein erfahrenerer Kollege Gureux sagt: “Eigentlich nicht. Dies gilt nur, wenn der PMOS normal als Verstärkerblock in der Schaltung arbeitet.”

Dadurch angespornt, befasst sich Neubean mit dem mathematischen Zusammenhang. Was wäre, wenn man das Verhalten zwischen Source und Gate des PMOS direkt modellieren könnte? Mit anderen Worten, was ist V(VS)/V(VG)? Neubean geht zur Tafel und schreibt die folgenden Gleichungen an:

Bild 4. High-Side-Messchaltung als Blockdiagramm.

Die Zerlegung der Schaltung in ein Steuersystem zeigt Bild 4. Der LTC2063, genau wie fast alle OPVs mit Spannungsrückkopplung, startet mit hoher DC-Verstärkung und einer Polstelle. Der OPV verstärkt das Fehlersignal und treibt das PMOS-Gate durch den RGATE–CGATE-Filter. CGATE und die PMOS-Source sind zusammen mit dem –IN-Eingang des OPV verbunden. RGAIN ist von diesem Schaltungsknoten aus mit der Source mit niedriger Impedanz verbunden. Selbst in Bild 4 könnte man annehmen, dass der RGATE–CGATE-Filter Stabilitätsprobleme verursacht, speziell wenn RGATE wesentlich größer ist als RGAIN. Letzten Endes treten bei der CGATE-Spannung, die direkt den Strom RGAIN im System beeinträchtigt, keine Änderungen am OPV-Ausgang auf.

Neubean bietet eine Erklärung dafür an, warum vielleicht RGATE und CGATE keine Instabilität hervorrufen: “Nun, die Gate-Source-Spannung ist fest und somit ist der RGATE–CGATE-Schaltkreis nicht relevant. Man muss lediglich das Gate einstellen und die Source folgt.“ Es ist ein Source-Folger.”

Sein erfahrenerer Kollege Gureux sagt: “Eigentlich nicht. Dies gilt nur, wenn der PMOS normal als Verstärkerblock in der Schaltung arbeitet.”

Dadurch angespornt, befasst sich Neubean mit dem mathematischen Zusammenhang. Was wäre, wenn man das Verhalten zwischen Source und Gate des PMOS direkt modellieren könnte? Mit anderen Worten, was ist V(VS)/V(VG)? Neubean geht zur Tafel und schreibt die folgenden Gleichungen an:

mit

mit

OPV-Verstärkung A und OPV-Pol ωA.

OPV-Verstärkung A und OPV-Pol ωA.

Neubean erkennt sofort den wichtigen Term gm. Was ist gm? Für einen MOSFET gilt

Neubean erkennt sofort den wichtigen Term gm. Was ist gm? Für einen MOSFET gilt

Bei einem Blick auf die Schaltung in Bild 1 geht Neubean ein Licht auf. Bei einem Strom von Null Ampere durch den Widerstand RSENSE sollte der Strom durch den PMOS ebenfalls Null Ampere betragen. Bei einem Strom von Null Ampere ist gm Null, da der PMOS effektiv ausgeschaltet ist, nicht genutzt wird und nicht vorgespannt ist und keine Verstärkung hat. Wenn gm = 0 ist VS/VE 0 bei 0 Hz und VS/VG 0 bei 0 Hz. Somit ist keine Verstärkung vorhanden und die Plots in Bild 3 können letztendlich gültig sein.

Instabilitäten mit dem LTC2063 versuchen

Gerüstet mit dieser Erkenntnis, probiert Neubean schnell ein paar Simulationen mit einem Strom ISENSE, der nicht gleich Null ist.

Bei einem Blick auf die Schaltung in Bild 1 geht Neubean ein Licht auf. Bei einem Strom von Null Ampere durch den Widerstand RSENSE sollte der Strom durch den PMOS ebenfalls Null Ampere betragen. Bei einem Strom von Null Ampere ist gm Null, da der PMOS effektiv ausgeschaltet ist, nicht genutzt wird und nicht vorgespannt ist und keine Verstärkung hat. Wenn gm = 0 ist VS/VE 0 bei 0 Hz und VS/VG 0 bei 0 Hz. Somit ist keine Verstärkung vorhanden und die Plots in Bild 3 können letztendlich gültig sein.

Instabilitäten mit dem LTC2063 versuchen

Gerüstet mit dieser Erkenntnis, probiert Neubean schnell ein paar Simulationen mit einem Strom ISENSE, der nicht gleich Null ist.

Bild 5. Frequenzverlauf von der Fehlerspannung zur Quell-Spannung bei einem Messstrom von ungleich Null.

Bild 5 zeigt, was wie ein wesentlich normalerer Verstärkungs/Phasen-Plot des Verlaufs von VE zu VS bei einem Übergang von >0 dB zu <0 dB aussieht. Bild 5 sollte etwa 2 kHz zeigen, mit reichlich PM bei 100 Ω, etwas weniger PM bei 100 kΩ und noch weniger mit 1 MΩ, aber nicht instabil.

Neubean geht ins Labor und wählt einen Messstrom mit dem High-Side-Messschaltkreis LTC2063. Er fügt einen RGATE mit hohem Widerstandswert ein, zuerst 100 kΩ und dann 1 MΩ, und erwartet ein instabiles Verhalten, zumindest aber eine Art Ringing. Doch leider ist das nicht der Fall.

Er versucht, den Drain-Strom im MOSFET zu erhöhen, indem er zuerst einen höheren ISENSE wählt, und dann einen kleineren Verstärkungswiderstand RGAIN. Nichts kann die Schaltung destabilisieren.

Bild 5. Frequenzverlauf von der Fehlerspannung zur Quell-Spannung bei einem Messstrom von ungleich Null.

Bild 5 zeigt, was wie ein wesentlich normalerer Verstärkungs/Phasen-Plot des Verlaufs von VE zu VS bei einem Übergang von >0 dB zu <0 dB aussieht. Bild 5 sollte etwa 2 kHz zeigen, mit reichlich PM bei 100 Ω, etwas weniger PM bei 100 kΩ und noch weniger mit 1 MΩ, aber nicht instabil.

Neubean geht ins Labor und wählt einen Messstrom mit dem High-Side-Messschaltkreis LTC2063. Er fügt einen RGATE mit hohem Widerstandswert ein, zuerst 100 kΩ und dann 1 MΩ, und erwartet ein instabiles Verhalten, zumindest aber eine Art Ringing. Doch leider ist das nicht der Fall.

Er versucht, den Drain-Strom im MOSFET zu erhöhen, indem er zuerst einen höheren ISENSE wählt, und dann einen kleineren Verstärkungswiderstand RGAIN. Nichts kann die Schaltung destabilisieren.

Bild 6. Zeitbereichsplot mit Schwingungen.

Er wendet sich erneut der Simulation zu und versucht, eine Phasenreserve mit einem Strom von ISENSE, der nicht Null ist, zu verringern. Selbst in der Simulation erscheint es schwierig, falls nicht unmöglich, Instabilität oder geringe Phasenreserve zu finden.

Neubean fragt Gureux, warum es ihm nicht gelingt, den Schaltkreis zu destabilisieren. Gureux rät ihm, sich die Zahlen genauer zu betrachten. Neubean ist Rätsel von Gureux gewohnt und untersucht, was die tatsächliche Polstelle in Verbindung mit RGATE und die gesamte Gate-Kapazität sein könnte. Bei 100 Ω und 250 pF liegt die Polstelle bei 6,4 MHz; mit 100 kΩ bei 6,4 kHz und mit 1 MΩ bei 640 Hz. Das Verstärkungs-Bandbreiten-Produkt (GBP) des LTC2063 beträgt 20 kHz. Wenn der LTC2063 mit Verstärkung betrieben wird, kann die Crossover-Frequenz bei geschlossenem Regelkreis leicht unter den Bereich des RGATE–CGATE-Pols gleiten.

Ja, Instabilität ist erreichbar

Bild 6. Zeitbereichsplot mit Schwingungen.

Er wendet sich erneut der Simulation zu und versucht, eine Phasenreserve mit einem Strom von ISENSE, der nicht Null ist, zu verringern. Selbst in der Simulation erscheint es schwierig, falls nicht unmöglich, Instabilität oder geringe Phasenreserve zu finden.

Neubean fragt Gureux, warum es ihm nicht gelingt, den Schaltkreis zu destabilisieren. Gureux rät ihm, sich die Zahlen genauer zu betrachten. Neubean ist Rätsel von Gureux gewohnt und untersucht, was die tatsächliche Polstelle in Verbindung mit RGATE und die gesamte Gate-Kapazität sein könnte. Bei 100 Ω und 250 pF liegt die Polstelle bei 6,4 MHz; mit 100 kΩ bei 6,4 kHz und mit 1 MΩ bei 640 Hz. Das Verstärkungs-Bandbreiten-Produkt (GBP) des LTC2063 beträgt 20 kHz. Wenn der LTC2063 mit Verstärkung betrieben wird, kann die Crossover-Frequenz bei geschlossenem Regelkreis leicht unter den Bereich des RGATE–CGATE-Pols gleiten.

Ja, Instabilität ist erreichbar

Bild 7. Normales Bodediagramm sobald man Strom zugibt, VE zu VS, mit schrecklicher Phasenreserve.

Indem er erkennt, dass das dynamische Verhalten des OPV sich bis in den Bereich des RGATE – CGATE Pols fortsetzen muss, wählt Neubean ein größeres GBP. Der 5-V-OPV LTC6255 passt direkt in die Schaltung mit einem höheren GBP von 6,5 MHz.

Eifrig versucht Neubean eine Simulation mit Strom, dem LTC6255, 100 kΩ Gate-Widerstand, und mit 300 mA Messstrom. Neubean macht dann weiter und bringt RGATE in die Simulation ein. Mit genügend RGATE kann eine zusätzliche Polstelle einen Schaltkreis destabilisieren.

Bild 6 und Bild 7 zeigt Simulationsergebnisse mit hohen RGATE-Werten. Bei einem konstanten Messstrom von 300 mA zeigt die Simulation Instabilität.

Laborergebnisse

Weil er sehen möchte, ob der Schaltkreis sich beim Messen eines Stromes von ungleich Null negativ verhalten könnte, probiert Neubean den LTC6255 mit einem stufenförmigen verlaufenden Laststrom und nutzt drei verschiedene RGATE-Werte. ISENSE geht von einer Basis von 60 mA auf einen höheren Wert von 220 mA über, ermöglicht durch einen Schalter, der mehr parallelen Lastwiderstand einbringt. Es gibt keine Nullstrom ISENSE-Messung, da bereits gezeigt wurde, dass die MOSFET-Verstärkung in diesem Fall zu niedrig ist.

In der Tat zeigt Bild 8 schließlich eine beeinträchtigte Stabilität mit Widerständen von 100 kΩ und 1 MΩ. Da die Ausgangsspannung stark gefiltert ist, wird die Gate-Spannung zum Detektor für Ringing. Ringing kennzeichnet eine geringe oder negative Phasenreserve und die Ringing-Frequenz bezeichnet die Übergangsfrequenz (Crossover Frequency).

Bild 7. Normales Bodediagramm sobald man Strom zugibt, VE zu VS, mit schrecklicher Phasenreserve.

Indem er erkennt, dass das dynamische Verhalten des OPV sich bis in den Bereich des RGATE – CGATE Pols fortsetzen muss, wählt Neubean ein größeres GBP. Der 5-V-OPV LTC6255 passt direkt in die Schaltung mit einem höheren GBP von 6,5 MHz.

Eifrig versucht Neubean eine Simulation mit Strom, dem LTC6255, 100 kΩ Gate-Widerstand, und mit 300 mA Messstrom. Neubean macht dann weiter und bringt RGATE in die Simulation ein. Mit genügend RGATE kann eine zusätzliche Polstelle einen Schaltkreis destabilisieren.

Bild 6 und Bild 7 zeigt Simulationsergebnisse mit hohen RGATE-Werten. Bei einem konstanten Messstrom von 300 mA zeigt die Simulation Instabilität.

Laborergebnisse

Weil er sehen möchte, ob der Schaltkreis sich beim Messen eines Stromes von ungleich Null negativ verhalten könnte, probiert Neubean den LTC6255 mit einem stufenförmigen verlaufenden Laststrom und nutzt drei verschiedene RGATE-Werte. ISENSE geht von einer Basis von 60 mA auf einen höheren Wert von 220 mA über, ermöglicht durch einen Schalter, der mehr parallelen Lastwiderstand einbringt. Es gibt keine Nullstrom ISENSE-Messung, da bereits gezeigt wurde, dass die MOSFET-Verstärkung in diesem Fall zu niedrig ist.

In der Tat zeigt Bild 8 schließlich eine beeinträchtigte Stabilität mit Widerständen von 100 kΩ und 1 MΩ. Da die Ausgangsspannung stark gefiltert ist, wird die Gate-Spannung zum Detektor für Ringing. Ringing kennzeichnet eine geringe oder negative Phasenreserve und die Ringing-Frequenz bezeichnet die Übergangsfrequenz (Crossover Frequency).

Bild 8. RGATE = 100 Ω, Strom von niedriger zu hoher Transiente. / Bild 9. RGATE = 100 Ω, Strom von hoher zu niedriger Transiente.

Bild 8. RGATE = 100 Ω, Strom von niedriger zu hoher Transiente. / Bild 9. RGATE = 100 Ω, Strom von hoher zu niedriger Transiente.

Bild 10. RGATE = 100 kΩ, Strom von niedriger zu hoher Transiente. / Bild 11. RGATE = 100 kΩ, Strom von hoher zu niedriger Transiente.

Bild 10. RGATE = 100 kΩ, Strom von niedriger zu hoher Transiente. / Bild 11. RGATE = 100 kΩ, Strom von hoher zu niedriger Transiente.

Bild 12. RGATE = 1 MΩ, Strom von niedriger zu hoher Transiente. / Bild 13. RGATE = 1 MΩ, Strom von hoher zu niedriger Transiente.

Ein Augenblick der Ideenfindung

Neubean wird sich bewusst, dass er viele High-Side-Messschaltkreis-ICs gesehen hat und es unglücklicherweise keine Chance für einen Ingenieur gibt, den Gate-Widerstand zu bestimmen, da sich alle Funktionen innerhalb des Bausteins befinden. Beispiele, die ihm in den Sinn kamen, waren die Hochvolt-/High-Side-Strommessbausteine AD8212, LTC6101, LTC6102 und LTC6104. Tatsächlich nutzt der AD8212 einen PNP-Transistor statt einen PMOS-FET. Er sagt Gureux, “Hey, es ist wirklich nicht wichtig, da moderne Bausteine dieses Problem bereits lösen.”

Als ob er diese Bemerkung erwartet hätte, und Neubean fast das Wort abschneidend, antwortet der Professor: “Angenommen du möchtest eine Kombination aus extrem niedrigem Versorgungsstrom und einen driftfreien Eingangsoffset, wie etwa in einem batteriegespeisten Messinstrument. Und du möchtest vielleicht einen LTC2063 oder LTC2066 als primären Verstärker einsetzen. Oder, vielleicht musst du einen niedrigen Strom messen, möglicherweise über einen Shunt mit 470 Ω und so genau und rauscharm wie möglich; in diesem Fall könntest du den ADA4528 einsetzen, der Rail-to-Rail-Eingangsverhalten hat. In diesen Fällen musst du dich mit der MOSFET-Treiberschaltung befassen.”

Und so…

Offensichtlich ist es dann möglich, die High-Side-Strommmessschaltung mit einem zu großen Gate-Widerstand zu destabilisieren. Neubean führt dieses Ergebnis auf seinen wohlwollenden Lehrer Gureux zurück. Gureux stellt fest, dass RGATE in der Tat die Schaltung destabilisieren kann, doch die anfängliche Unfähigkeit, dieses Verhalten herauszufinden, resultierte aus einem falsch formulierten Problem. Es muss Verstärkung vorhanden sein, was in dieser Schaltung erforderlich ist, um ein Non-Zero-Signal zu messen.

Gureux antwortet: “Sicher, wenn ein Pol die Phasenreserve bei einem Übergang (Crossover) negativ beeinträchtigt, entsteht Ringing. Doch dein hinzugefügter Gate-Widerstand von 1 MΩ ist absurd — selbst 100 kΩ ist verrückt. Denke daran, es ist immer gut zu versuchen, den Ausgangsstrom eines OPV zu begrenzen, falls er versucht, eine Gate-Kapazität von einer zur anderen Versorgungsschiene zum Schwingen zu bringen.

Neubean stimmt zu. “Welchen Widerstandswert verwende ich also?” Gureux bemerkt zuversichtlich: “100 Ω”.

Bild 12. RGATE = 1 MΩ, Strom von niedriger zu hoher Transiente. / Bild 13. RGATE = 1 MΩ, Strom von hoher zu niedriger Transiente.

Ein Augenblick der Ideenfindung

Neubean wird sich bewusst, dass er viele High-Side-Messschaltkreis-ICs gesehen hat und es unglücklicherweise keine Chance für einen Ingenieur gibt, den Gate-Widerstand zu bestimmen, da sich alle Funktionen innerhalb des Bausteins befinden. Beispiele, die ihm in den Sinn kamen, waren die Hochvolt-/High-Side-Strommessbausteine AD8212, LTC6101, LTC6102 und LTC6104. Tatsächlich nutzt der AD8212 einen PNP-Transistor statt einen PMOS-FET. Er sagt Gureux, “Hey, es ist wirklich nicht wichtig, da moderne Bausteine dieses Problem bereits lösen.”

Als ob er diese Bemerkung erwartet hätte, und Neubean fast das Wort abschneidend, antwortet der Professor: “Angenommen du möchtest eine Kombination aus extrem niedrigem Versorgungsstrom und einen driftfreien Eingangsoffset, wie etwa in einem batteriegespeisten Messinstrument. Und du möchtest vielleicht einen LTC2063 oder LTC2066 als primären Verstärker einsetzen. Oder, vielleicht musst du einen niedrigen Strom messen, möglicherweise über einen Shunt mit 470 Ω und so genau und rauscharm wie möglich; in diesem Fall könntest du den ADA4528 einsetzen, der Rail-to-Rail-Eingangsverhalten hat. In diesen Fällen musst du dich mit der MOSFET-Treiberschaltung befassen.”

Und so…

Offensichtlich ist es dann möglich, die High-Side-Strommmessschaltung mit einem zu großen Gate-Widerstand zu destabilisieren. Neubean führt dieses Ergebnis auf seinen wohlwollenden Lehrer Gureux zurück. Gureux stellt fest, dass RGATE in der Tat die Schaltung destabilisieren kann, doch die anfängliche Unfähigkeit, dieses Verhalten herauszufinden, resultierte aus einem falsch formulierten Problem. Es muss Verstärkung vorhanden sein, was in dieser Schaltung erforderlich ist, um ein Non-Zero-Signal zu messen.

Gureux antwortet: “Sicher, wenn ein Pol die Phasenreserve bei einem Übergang (Crossover) negativ beeinträchtigt, entsteht Ringing. Doch dein hinzugefügter Gate-Widerstand von 1 MΩ ist absurd — selbst 100 kΩ ist verrückt. Denke daran, es ist immer gut zu versuchen, den Ausgangsstrom eines OPV zu begrenzen, falls er versucht, eine Gate-Kapazität von einer zur anderen Versorgungsschiene zum Schwingen zu bringen.

Neubean stimmt zu. “Welchen Widerstandswert verwende ich also?” Gureux bemerkt zuversichtlich: “100 Ω”.Autorenvorstellung: Aaron Schultz [aaron.schultz@analog.com] ist Applikationsingenieur-Manager in der LPS Business Unit bei © Analog Devices. Seine verschiedenen System-Engineering-Funktionen im Design und im Applikationsbereich brachten ihn mit unterschiedlichen Schwerpunkten zusammen. Angefangen bei Batteriemanagement, Photovoltaik, dimmbare LED-Treiberschaltungen, Niedervolt- und Hochstrom-DC/DC-Wandlung, High-Speed Glasfaserkommunikation, R&D für fortschrittliches DDR3 Memory, Kundentoolentwicklung, Validierung und Basis-Analogschaltkreise, während er über die Hälfte seiner beruflichen Laufbahn im Bereich Leistungswandlung zubrachte. Er hat 1993 sein Studium an der Carnegie Mellon University abgeschlossen und MIT im Jahr 1995.