© linear technology

Application Notes |

Probleme am I2C meistern

I2C ist ein populärer 2-Drahtbus für die Verbindung zwischen ICs. Er ist einfach einzusetzen und arbeitet mit bis zu 400 kHz.

Einleitung

Jedoch, wie oft bei Standards, kann es zu Problemen kommen, wenn man die originalen I2C Spezifikation ausreizt oder diese für aktuelle Systemanforderungen nicht ausreichen. Mit der zunehmenden Komplexität sind mehr und mehr I2C Bausteine am Bus, was zu Kompromissen bei einigen Parametern führen kann.

Die meisten Probleme bei I2C System sind elektrischer Natur oder liegen im Timing bzw. in der Signalqualität. Sie treten bei Systemgrößen auf, bei denen die maximale Buskapazität von 400pF überschritten wird, durch Inkompatibilität älterer nicht konformer oder unbekannter I2C ICs oder bei Bussen, die auf unerklärliche Weise auf Low bleiben oder einfach dann, wenn nicht genug Device Adressen verfügbar sind.

Dieser Artikel zeigt wie man mit I2C Controllern von Linear Technology alle diese Probleme gleichzeitig lösen und sich so auf das Schaltungsdesign konzentrieren kann, ohne die Einschränkungen durch die Limits des I2C Standards und dessen Fallstricke.

Strenge Anforderungen erfüllen

Der I2C Standard spezifiziert eine maximale Buskapazität von 400 pF. Leiterzüge, lange Leitungen und Busknoten bringen zusätzliche Kapazität auf den Bus, was es speziell in großen Systemen schwierig macht, die 400pF Begrenzung einzuhalten. Eine weitere Einschränkung ist, dass I2C Bausteinen mit unterschiedlichen Versorgungsspannungen nicht denselben Bus nutzen dürfen.

Einige Systeme erfordern auch das Aus- und Einstecken von I/O Boards im laufenden Betrieb das kann die Kommunikation auf der Backplane stören, falls keine Gegenmaßnahmen getroffen werden. Beachtet man diese Problemquellen nicht, kann dies die I2C Konformität, die Datenintegrität und die Zuverlässigkeit des Systems beeinträchtigen. I2C Busbuffer lösen diese grundlegenden Probleme. Sie bieten kapazitive Bufferung-, Levelshifting- und Hot Swapp-Fähigkeit durch das Pre-Biasing der Busleitungen.

Mit stetig wachsender Systemgröße, entstehen neue elektrische Probleme und es stellt sich heraus, dass die Vorteile älterer Busbuffer zulasten bestimmter I2C Spezifikationen gehen. Busbuffer müssen unterscheiden können zwischen dem low Zustand einer extern ansteuernden Logik und dem low Zustand der eigenen Logik. Dies brachte Buffer, deren Ausgänge Low Pegel (VOL) oberhalb der 0,4 V der I2C Spezifikation liefern oder Buffer, deren VOL mit einem Offset überlagert ist. Je mehr von diesen alten Buffern am Bus sind, umso kleiner ist der Störabstand bei Low-Pegel, was die Empfindlichkeit des Busses gegenüber Störungen erhöht. Größere Systeme profitieren von nahezu idealen Bus-Buffern, mit denen der Logic-Low Störabstand der I2C Spezifikation wiedererlangt wird. D.h. ein fast idealer Bus-Buffer ist ein schneller Buffer, der aktiv ist bis die Busspannung den Wert von 0,3 VCC (VIL) durchläuft und somit keine zusätzliche Bus Last bringt. Eine zusätzliche Anforderung an große Systeme ist die Rückwärtskompatibilität zu Buffern deren Anstiegszeitbeschleuniger (RTAs) unter 0,3 VCC einschalten oder mit Buffern, die einen nichtkonformen VOL Pegel von 0,6 V treiben. Bild 2 zeigt den LTC4315 von Linear Technology, ein neuer Busbuffer, der alle angesprochenen Probleme bewältigt. Der LTC4315 löst gewöhnlich große Buskapazitäten in kleine Segmente von <400 pF auf, sein Levelshifter arbeitet an Busversorgungen von 1,4 V bis 5,5 V und er bietet Hot Swap Fähigkeit, wodurch I/O Karten im laufenden Betrieb gewechselt werden können. Fast noch wichtiger ist sein großer Eingangs-Störabstand durch einen Low-Pegel VIL= 0,3 * Vcc , womit so stets ein ausreichend großer Störabstand bei Logic Low vorliegt. Damit können ohne weiteres mehrere LTC4315s kaskadiert werden, ohne dass sich der Störabstand verringert - perfekt für große oder rauschbehaftete Systeme. Der LTC4315 kann zusammen mit Bausteinen eingesetzt werden, die mit hoher VOL > 0,4 V arbeiten und solchen, die bei Pegeln < 0,3*VCC das RTAS einschalten. Somit können Systeme gebaut werden, an die beliebige I2C Bausteine angeschlossen werden können. Schlechtes Timing vermeiden In I2C Systemen gibt es zwei wesentliche Timing Probleme. Zum einen wird die Signalanstiegszeit (Slew-Rate) hauptsächlich durch die I2C Bus Pull-up Widerstände bestimmt, die manchmal zu hochohmig sind, wenn kürzere Bus Anstiegszeiten gefordert sind, wie z.B. im Falle der PICMG Spezifikationen. Diese verlangen SCL und SDA Signale mit einer Anstiegszeit von 1 V auf 2,3 V innerhalb von 900 ns bei 2,7 kΩ Pull-up Widerstand nach 3,3 V und einer Lastkapazität von 690 pF. Andererseits können große Buskapazitäten und begrenzte Pull-Up-Ströme die Anstiegszeiten kritisch verlängern bis zu einem Punkt, an dem die maximalen Anstiegszeiten laut den I2C Spezifikation von 1 µs bei 100 kHz oder 300 ns bei 400 kHz nicht eingehalten werden.Figure 1 -----

Figure 2 ----- Alle Grafiken haben eine Zoom-Funktion.

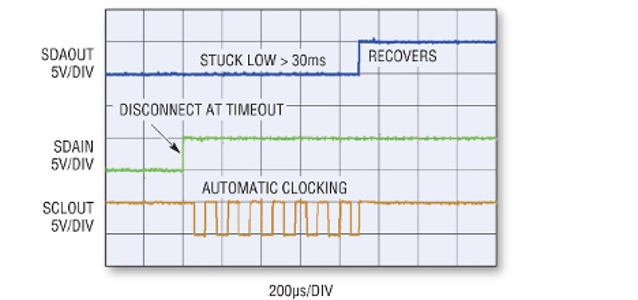

Linear Technology bietet verschiedene Busbuffer mit wählbarer Anstiegszeitbeschleunigung, wie den LTC4315 oder den LTC4311, ein Stand-alone Anstiegszeitbeschleuniger, der einfach parallel an den Bus angehängt wird. Diese autonomen Anstiegszeitbeschleuniger bieten hohe anstiegsbegrenzte Pull-up Ströme, die alle Slew-Rate Anforderungen erfüllen. Die Beschleuniger werden nur während eines positiven Signalanstiegs auf dem Bus automatisch aktiviert, und erhöhen die Anstiegsgeschwindigkeit auf eine bestimmte Rate, welche die Board- und die System Zuverlässigkeit erhöht. Dies geschieht durch einen sanften und kontrollierten Übergang während der Anstiegsflanken. Die Systeme reagieren auch weniger empfindlich auf Störungen bei ansteigenden Flanken, da durch den Beschleuniger die Pull-up Impedanz niedriger ist, als mit den Pull-up Widerständen alleine. Die Beschleuniger ermöglichen damit den Einsatz großer Pull-Ups, was den Stromverbrauch reduziert und den Rauschabstand verbessert. Ein weiteres Timing Problem ist das Hängenbleiben des I2C Bus auf Low. Symptome hierfür sind Kommunikationsprobleme, Daten mit vielen Nullen und ungewöhnliches GUI Verhalten. Das „auf Masse hängen bleiben“ von SCL oder SDA liegt an I2C Bus Bausteinen, die sich fehlerhaft verhalten. Wird das nicht korrigiert, blockiert das auf Low hängende IC alle anderen Teilnehmer am Bus bis das blockierenden IC High Pegel ausgibt. Wenn der Bus auf Low hängt, muss der Host manuell eingreifen, meist durch einen Reset, was aber störend und u.U. teuer ist und Zeit kostet. Das Problem blockierter Busse kann einfach durch den Einsatz von Busbuffern von Linear Technology gelöst werden, die über wählbaren Busschutz verfügen wie der LTC4315, der die SDA und SCL Ausgänge laufend auf einen Low Status von länger als 30 ms überwacht (Bild 3). Tritt dies ein, werden die Eingangs- zu-Ausgangsverbindungen beider I2C Signale unterbrochen, was eine weitere Kommunikation mit den blockierten Bauteilen stoppt. Der Busbuffer generiert bis zu 16 Taktimpulse am SCLOUT Pin um den blockierten lokalen Bus freizugeben. Ist dieser nicht mehr blockiert, oder die 16 Taktimpulse sind durchlaufen, wird ein Stopp Bit erzeugt um den Bus für weitere Kommunikation freizugeben. Auch werden die Eingangs- zu-Ausgangsverbindungen beider I2C Signale wieder hergestellt, aber nur, wenn der Bus im Idle-Modus ist und sich nicht gerade in einer I2C Transaktion befindet. Signalisierung vereinfachen Die 111 physikalischen Adressen des Standard I2C Buses sind meistens ausreichend, größere Systeme jedoch, müssen oft die Kommunikation für mehr als 111 Bauteile ermöglichen. Systemdesigner müssen oft auch Slave Bausteine einsetzen, die nur über wenige Adressen verfügen, was zur Mehrfachbelegung derselben Adresse zwingt (nested addressing). Hier sollten I2C Multiplexer von Linear Technology verwendet werden, um die Mehrfachverwendung von physikalischen I2C Adressen zu ermöglichen. Der bi-direktionalen Natur dieser Multiplexer wegen, können sie auch verwendet werden, um I2C Daten von den Ausgangsbussen zu den Eingangsbussen zu übertragen. Bild 4 zeigt den LTC4314, ein pin-selektierbarer 4:1 I2C Multiplexer, bei dem vier I2C Bausteine unter derselben Adresse laufen. Die einzelnen Enable Pins ermöglichen es dem Anwender auszuwählen, welche Downstream Busse an dem Upstream Bus verwendet werden. Auch ist ein LTC4306 mit 1:4 Software-selektierbarem Multiplexer verfügbar, der in gleicher Weise arbeitet, jedoch per I2C Befehl anstelle von Enable-Pins gesteuert wird. Diese I2C Multiplexer haben integrierte Busbuffer, und so alle Merkmale der Linear Technology Busbuffer wie der große Rauschabstand, die Anstiegszeitbeschleunigung und den Schutz vor Blockieren der Busse. Schlussbemerkung Der über 30 Jahre alte Bus wird noch verbreitet eingesetzt, wogleich die Systeme größer und komplexer werden, was eine Herausforderung an die Spezifikationen und deren Grenzen bedeutet. Designer können bei der Entwicklung die Anforderungen bezüglich elektrischer Probleme und solcher durch Timing und die Signalisierung berücksichtigen, besser ist es aber, durch vorbeugende Maßnahmen die gezeigten Probleme auszuschalten, da man nie weis welche I2C Bauteile letztendlich im System verwendet werden – z.B. nicht konforme I2C ICs oder solche, die den Bus blockieren. Die I2C Spezifikationen kann man sehr einfach einhalten, setzt man von vorne herein die richtige Kombination von I2C Busbuffern, Anstiegszeitbeschleunigern und Multiplexern von Linear Technology ein. Dann kann man auch später ein System ohne Einschränkungen und ohne Verzögerungen erweitern. ----- Autor: Chris Gobok, Product Marketing Engineer, Mixed Signal Products, © Linear TechnologyFigure 3 -----

Figure 4 ----- Alle Grafiken haben eine Zoom-Funktion.