Salience Labs wirbt 11,5 Millionen USD für KI-Chips ein

Salience Labs hat eine erste Finanzierungsrunde in Höhe von 11,5 Millionen US-Dollar abgeschlossen, um einen ultraschnellen Multi-Chip-Prozessor zu entwickeln, der Photonik und Elektronik kombiniert und so die exponentiellen Fortschritte der künstlichen Intelligenz (KI) vorantreiben soll. Angeführt wurde die Runde von Cambridge Innovation Capital und Oxford Science Enterprises, unter Beteiligung von Oxford Investment Consultants, dem ehemaligen CEO von Dialog Semiconductor Jalal Bagherli, Silicon Catalyst, dem Goh Family Office in Singapur und dem von Arm unterstützten Deeptech Labs.

Die Anforderungen an die Geschwindigkeit von KI-Berechnungen verdoppeln sich alle 3,4 Monate und bringen damit herkömmliche Halbleitertechnologien an ihre Grenzen. Jetzt entwickelt sich der Markt für KI-Geräte von universellen Anwendungen hin zur Lösung spezifischer Aufgaben. Um den Fortschritt in der KI in allen Branchen deutlich zu beschleunigen, ist ein völlig neuer Ansatz für die Datenverarbeitung erforderlich. Dieser Ansatz muss sowohl skalierbarer als auch stark anwendungsorientiert sein.

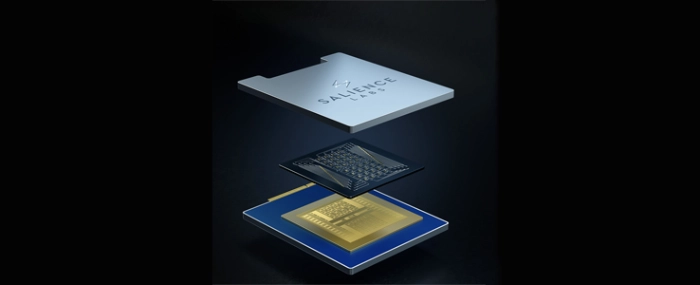

Das Start-up Salience Labs wurde 2021 aus der WWU Münster und der University of Oxford ausgegliedert, um einen ultraschnellen Multi-Chip-Prozessor zu entwickeln, der Photonik mit Standardelektronik kombiniert. Die skalierbare Technologie von Salience Labs liefert eine hochparallele und effiziente Datenverarbeitung, bei der durch Ausnutzung eines breiten Farbspektrums bis zu 64 Vektoren gleichzeitig in einem Lichtstrahl genutzt werden können.

Salience Labs verwendet einen eigens entwickelten, amplitudenbasierten Ansatz für die Photonik, der mit Taktraten von mehreren 10 GHz eine extrem hohen Rechendichte liefert. Zusammen mit der gleichzeitigen Ausführung vieler Rechenoperationen ermöglicht er Leistungen im ExaOp-Bereich. Dies eröffnet Möglichkeiten für eine Vielzahl neuer und bestehender KI-Prozesse und -Anwendungen.

„Auf der Grundlage unserer Forschungen an den Universitäten Münster und Oxford haben wir einen radikal neuen Ansatz für photonisches Rechnen gewählt und eine neue Multi-Chip-Architektur für photonisches ‚On-Memory-Computing‘ entwickelt. Unser einzigartiger Ansatz liefert einen extrem leistungsfähigen Prozessorchip, der im Vergleich zu herkömmlichen elektronischen Chips auf weniger Fläche ein Vielfaches an Leistung erzielt, ohne dass die Photonik auf große Dimensionen skaliert werden muss“, sagt Johannes Feldmann, CTO und Mitgründer von Salience Labs.

Das Unternehmen nutzt ein Multi-Chip-Design, bei dem die photonische Verarbeitung direkt über dem Static Random Access Memory (SRAM) des elektronischen Chips ausgeführt wird. Diese neuartige „On-Memory Compute“-Architektur minimiert den Datentransfer und ist dadurch grundlegend schneller. Sie ist an die anwendungsspezifischen Anforderungen verschiedener Marktsegmente anpassbar und eignet sich daher hervorragend für datenintensive KI-Aufgaben, wie sie beispielsweise in den Bereichen Kommunikation, Robotik, Bildverarbeitung und Gesundheitswesen vorkommen.

„Das Team von Salience Labs kombiniert kommerziellen und technischen Scharfsinn mit einer revolutionären Marktvision. Die einzigartige ‚On-Memory-Compute‘-Architektur ist wegweisend und hat das Potenzial für bahnbrechende Leistungs- und Energieeffizienz, die über das hinausgeht, was etablierte CMOS-Architekturen bieten“, so Jalal Bagherli, Investor von Salience Labs und ehemaliger CEO von Dialog Semiconductor.

„Die Welt benötigt immer schnellere Chips, um die Fähigkeiten von KI zu steigern, doch die Halbleiterindustrie kann mit der hohen Nachfrage nicht Schritt halten. Wir lösen das Problem mit unserer eigens entwickelten ‚On-Memory-Compute‘-Architektur, die die ultraschnelle Geschwindigkeit der Photonik, die Flexibilität der Elektronik und die etablierte Fabrikation von CMOS kombiniert“, sagt Vaysh Kewada, CEO und Mitgründerin von Salience Labs.