Continuous Time Sigma-Delta Wandler eine neue Möglichkeit die „Signal Chain“ zu optimieren

Viele Anwendungen benötigen heutzutage einen immer kleineren Formfaktor bei gleichbleibenden Ansprüchen an die Performance.

Entwickler stehen hier oft vor der Frage, wie das zu realisieren ist und müssen mit Kompromissen zurechtkommen. Das heißt, um eine Reduzierung des Formfaktors zu erreichen, muss meistens auf Kosten des Rauschverhaltens oder der Genauigkeit Abstriche gemacht werden.

Um eine möglichst optimale Ausbeute des gewünschten Sensors/Signals zu erreichen, müssen alle Bausteine in der Signalkette perfekt aufeinander abgestimmt werden. Vom Sensor bis zum Analog-Digital Wandler kommen hierbei meist mehrere diskrete Bauelemente zum Einsatz. Neben Sensor und ADC werden oft Instrumentenverstärker, ADC-Treiber, Referenz-Buffer und Filter verwendet. Besonders die Auswahl des passenden ADC-Treibers und das Filterdesign sind hier Fehlerquellen, die oft unterschätzt werden.

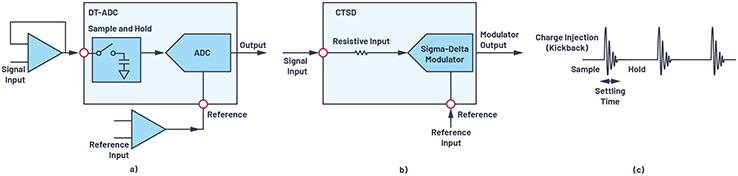

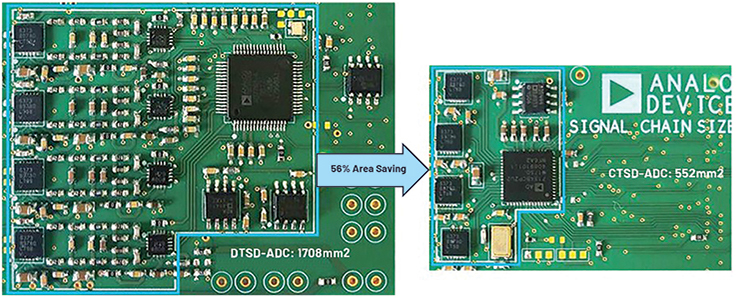

Eine Möglichkeit, das Design zu optimieren, die Bill of Materials (BOM) und den Formfaktor zu reduzieren sind µModule. Bei µModulen handelt es sich um hochintegrierte Lösungen, welche neben dem Wandler auch Buffer und Passive Komponenten enthalten. Eine weitere, neue Option bilden die sogenannten Continuous Time Sigma-Delta Konverter (CTSD). Bei dieser neuen Technologie ist es möglich den ADC direkt zu treiben ohne einen Verstärker als Buffer verwenden zu müssen. Des Weiteren ermöglicht die neue Topologie eine Vereinfachung des Filterdesigns. Abbildung 1 zeigt den Unterschied zwischen den traditionellen Discrete Time ADCs (DT-ADC) und CTSD Konvertern. Im Vergleich zu den traditionellen Designs kann bei CTSD eine Reduzierung des Formfaktors von bis zu 68% erzielt werden.

Bei traditionellen DT-ADCs, wie beispielweise SAR ADCs oder Sigma-Delta ADCs, kommt die sogenannte „switch-cap“ Topologie zum Einsatz. Diese befindet sich an den Eingängen des ADCs und der Referenz. Dabei unterscheidet man zwischen zwei verschiedenen Phasen, der „Sample“ und „Hold“ Phase. Hierbei kommt es zu einem Laden und Entladen des „Hold“ Kondensators. Es muss also genügend Strom zum Laden und Entladen bereitgestellt und aufgrund von parasitäre Eigenschaften Ladung absorbiert werden können (charge injection kick-back). Viele Sensoren haben nicht die Möglichkeit solch hohe Ströme bereitzustellen, wodurch ein Buffer benötigt wird. Neben dieser Funktion muss der Treiber auch schnell genug sein (kleine settling time, hohe slew rate), damit der Ausgang am Ende der „Sample“ Phase (Abb. 1c) eingeschwungen ist, um keine zusätzlichen Fehler in das gewünschte Signal einzubringen. Damit stellen sich sehr hohe Anforderungen an den ADC Treiber.

Ein CTSD Wandler hat einen resistiven Eingang und kann direkt vom Sensor getrieben werden. Kann der Sensor den ADC nicht treiben (z.B. wenn der Sensor sehr hochohmig ist), ist es möglich einen einfachen Verstärker zur Impedanz Wandlung dazwischenzuschalten.

Ein weiterer Vorteil der CTSD ist die inhärente Antialiasing Filter Eigenschaft (Tiefpass). Bei traditionellen Topologien wird ein Tiefpass an den Eingängen benötigt, um hoch frequente unerwünschte Signale zu filtern. Der Grund hierfür ist das Nyquist Kriterium. Dies besagt, dass die Abtastrate mindestens doppelt so groß sein muss, wie die Nutzfrequenz. Ist die Abtastrate geringer kann es zum Aliasing kommen, und unerwünschtes Rauschen in das Signal gefaltet werden. Eine Erklärung für die inhärenten Antialiasing Filter Eigenschaften bei CTSD Wandlern ist, dass das Abtasten nicht direkt am Eingang des Modulators stattfindet, sondern nach dem sogenannten „loop filter“.

Fazit: Die CTSD Topologie bietet neben den traditionellen Architekturen eine weitere, neue Möglichkeit Signalketten zu optimieren. Spielen zudem Time to Market, BOM oder Formfaktor eine wichtige Rolle, bilden ADCs wie der AD4134 eine gute Alternative. Durch die resistiven Eingänge und inhärenten Filter Eigenschaften, können so viele Designs vereinfacht und optimiert werden. In vielen Applikationen fallen damit ADC Treiber, Passive für das Filterdesign und Referenz Buffer weg. Zu der ganzen Thematik gibt es auf Analog Dialogue eine komplette Serie an technischen Artikeln, welche die genannten Vorteile und noch viele weitere Features näher betrachten.

About the Author: Benjamin Reiss has been working at © Analog Devices in Munich, Germany since April 2017. He graduated in 2016 from the Friedrich-Alexander University in Erlangen with a master’s degree in nanotechnology. After completion of the trainee program at Analog Devices, he joined the regional team as a field applications engineer supporting several broad market accounts. He can be reached at benjamin.reiss@analog.com.