© farang dreamstime.com

Application Notes |

Stand des Isolation Design Flows und der partiellen Rekonfiguration für Zynq 7000 / Zynq UltraScale+

FPGAs (Field Programmable Gate Arrays) sind integrierte Schaltkreise der Digitaltechnik und kommen in vielen Gebieten der digitalen Elektronik zum Einsatz. Aufgrund ihrer immer weiter ansteigenden Leistungsfähigkeit und Geschwindigkeit werden sie immer häufiger auch zur Beschleunigung von Berechnungen in Großrechenzentren verwendet.

Von der einfachen Verknüpfung elektrischer Signale bis hin zur Realisierung komplexer logischer Funktionen, wie z. B. hochsicherer Datenverschlüsselung, ist ein FPGA in der Lage, Aufgaben mit sehr hoher Geschwindigkeit und Parallelität abzuarbeiten. Durch die Vereinigung diverser digitaler Funktionen auf nur einem FPGA-Chip, wird die Leistungsfähigkeit einer Schaltung drastisch erhöht und der Platzbedarf minimiert. Auch in sicherheitsrelevanten Anwendungen ist der Einsatz von FPGAs mehr und mehr im Kommen.

Im Folgenden wird ein Konzept vorgestellt, mit dem die IT-Sicherheit von FPGAs weiter erhöht werden kann. Mit dem Isolation Design Flow (IDF) kann die VHDL-Logik in separate isolierte Zonen aufgeteilt werden. Es wird gezeigt, wie diese in Vivado 2018.2 für Zynq 7000 und Zynq UltraScale+ möglich ist.

Anschließend wird geprüft, ob der IDF mit der partiellen Rekonfiguration kombinierbar ist und damit Algorithmen im laufenden Betrieb in die gewünschten isolierten Zonen nachgeladen werden können.

1. Isolation Design Flow

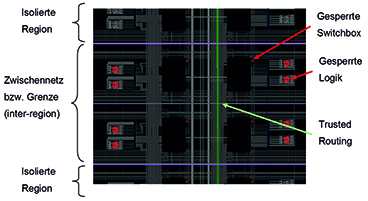

Der Isolation Design Flow fügt einem bestehenden Design nachträglich isolierte Zonen hinzu, die entweder gar nicht oder nur über ein spezielles "Trusted Routing" miteinander kommunizieren.

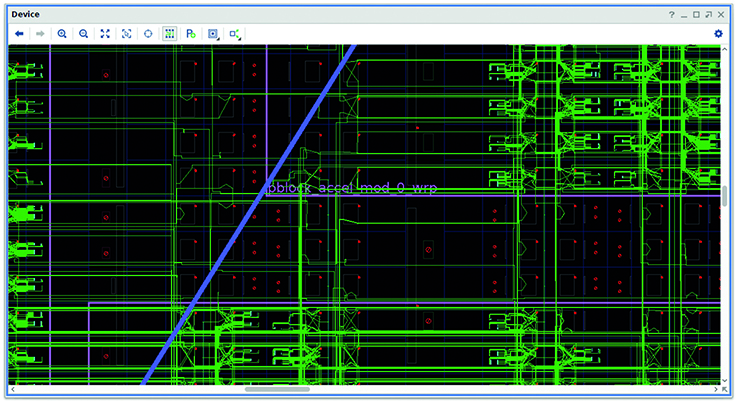

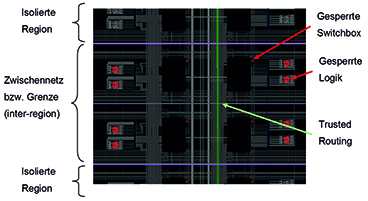

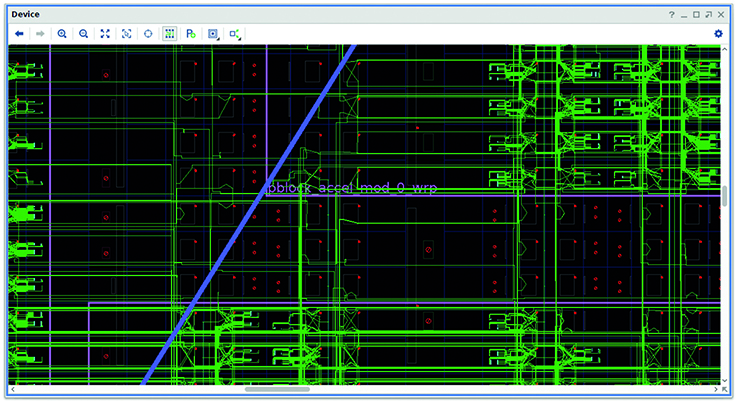

Abbildung 1: Regionen in einem FPGA werden durch physikalische Grenzen voneinander getrennt. Nur Verbindungen, die die Vorgaben des Trusted Routings einhalten, dürfen durch die festgelegten Grenzen verlaufen.

Für den IDF muss bei einem Blockdesign zunächst mit Wrappern eine Hierarchie erzeugt werden. Bei den Wrappern wird anschließend die Eigenschaft HD.ISOLATED aktiviert und für die Platzierung der Logik spezielle PBlöcke vorgegeben, die einen Mindestabstand von einem Tile aufweisen müssen.

Nach einer zusätzlichen Sperrung aller Logikelemente und Switchboxen zwischen den PBlöcken in der sogenannten Fence, bildet Vivado das Trusted Routing als direkte Verbindungen ohne Abzweige zwischen den PBlöcken aus (vgl. Abbildung 1).

1.1 Aktueller Stand beim VIV

Der Isolation Design Flow fügt einem bestehenden Design nachträglich isolierte Zonen hinzu, die entweder gar nicht oder nur über ein spezielles "Trusted Routing" miteinander kommunizieren.

Abbildung 1: Regionen in einem FPGA werden durch physikalische Grenzen voneinander getrennt. Nur Verbindungen, die die Vorgaben des Trusted Routings einhalten, dürfen durch die festgelegten Grenzen verlaufen.

Für den IDF muss bei einem Blockdesign zunächst mit Wrappern eine Hierarchie erzeugt werden. Bei den Wrappern wird anschließend die Eigenschaft HD.ISOLATED aktiviert und für die Platzierung der Logik spezielle PBlöcke vorgegeben, die einen Mindestabstand von einem Tile aufweisen müssen.

Nach einer zusätzlichen Sperrung aller Logikelemente und Switchboxen zwischen den PBlöcken in der sogenannten Fence, bildet Vivado das Trusted Routing als direkte Verbindungen ohne Abzweige zwischen den PBlöcken aus (vgl. Abbildung 1).

1.1 Aktueller Stand beim VIV

Ob die Isolation erfolgreich durchgeführt werden konnte, kann mit dem VIV (Vivado Isolation Verifier) überprüft werden.

Dieser musste in Vivado 2017.2 noch als separates Script nachgeladen werden und existierte hier nur für den Zynq 7000.

In Vivado 2018.2 ist der VIV fester Bestandteil im Design Rule Check (DRC) und muss nur über den Befehl set_param hd.enableIDFDRC true aktiviert werden. Nach der Implementation stehen dann zusätzliche Prüfungen im DRC im Bereich der Isolation zur Verfügung (vgl. Abbildung 2).

Abbildung 2: Aktivierung des VIV im DRC.

2. Partielle Rekonfiguration und Isolation Design Flow

Ob die Isolation erfolgreich durchgeführt werden konnte, kann mit dem VIV (Vivado Isolation Verifier) überprüft werden.

Dieser musste in Vivado 2017.2 noch als separates Script nachgeladen werden und existierte hier nur für den Zynq 7000.

In Vivado 2018.2 ist der VIV fester Bestandteil im Design Rule Check (DRC) und muss nur über den Befehl set_param hd.enableIDFDRC true aktiviert werden. Nach der Implementation stehen dann zusätzliche Prüfungen im DRC im Bereich der Isolation zur Verfügung (vgl. Abbildung 2).

Abbildung 2: Aktivierung des VIV im DRC.

2. Partielle Rekonfiguration und Isolation Design Flow

Die partielle Rekonfiguration bezeichnet den Vorgang bei dem die Inhalte eines PBlocks in einem FPGA-Design im laufenden Betrieb nachgeladen werden.

Auf ein bestehendes Blockdesign kann ein spezieller TCL Flow angewandt werden, um die benötigten partiellen und statischen Bitströme zu einem Design zu erzeugen. Xilinx verkündet offiziell auf seiner Webseite, dass es möglich ist, den Isolation Design Flow und die partielle Rekonfiguration im selben Design zu vereinen.

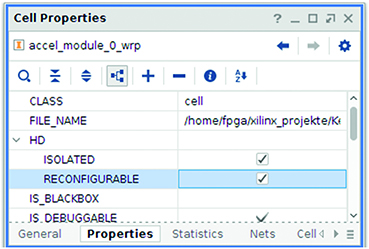

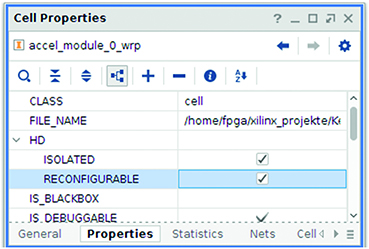

Der praktische Test zeigt, dass beim selben Design beim selben Wrapper die Eigenschaft HD.ISOLATED und die Eigenschaft HD.RECONFIGRUABLE gleichzeitig aktiviert werden können (vgl. Abbildung 3).

Abbildung 3: Aktivierung von IDF und PR beim selben Wrapper.

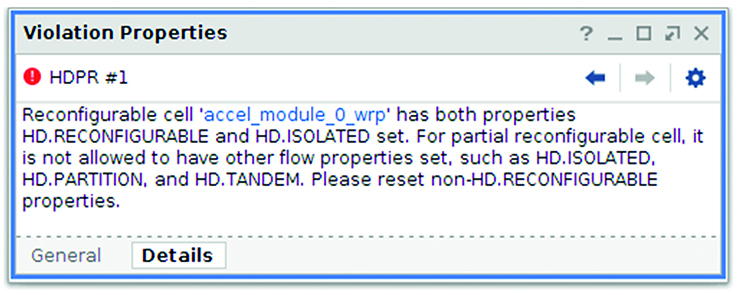

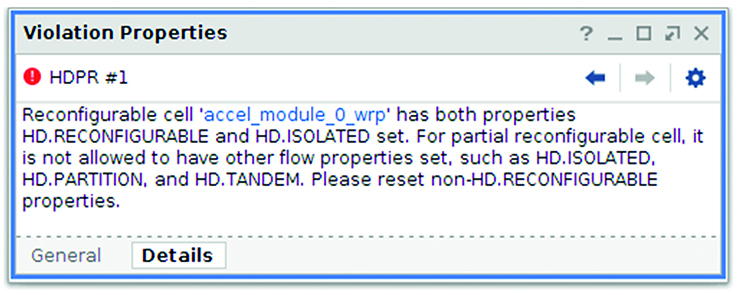

Der DRC führt bei der gleichzeitigen Aktivierung jedoch zu einer Fehlermeldung und die Implementation kann nicht fehlerfrei durchgeführt werden (vgl. Abbildung 4).

Die partielle Rekonfiguration bezeichnet den Vorgang bei dem die Inhalte eines PBlocks in einem FPGA-Design im laufenden Betrieb nachgeladen werden.

Auf ein bestehendes Blockdesign kann ein spezieller TCL Flow angewandt werden, um die benötigten partiellen und statischen Bitströme zu einem Design zu erzeugen. Xilinx verkündet offiziell auf seiner Webseite, dass es möglich ist, den Isolation Design Flow und die partielle Rekonfiguration im selben Design zu vereinen.

Der praktische Test zeigt, dass beim selben Design beim selben Wrapper die Eigenschaft HD.ISOLATED und die Eigenschaft HD.RECONFIGRUABLE gleichzeitig aktiviert werden können (vgl. Abbildung 3).

Abbildung 3: Aktivierung von IDF und PR beim selben Wrapper.

Der DRC führt bei der gleichzeitigen Aktivierung jedoch zu einer Fehlermeldung und die Implementation kann nicht fehlerfrei durchgeführt werden (vgl. Abbildung 4).

Abbildung 4: Fehler bei IDF und PR beim selben Wrapper.

Auf Nachfrage teilte Xilinx mit, dass IDF und PR zwar im gleichen Design, jedoch nicht beim gleichen Wrapper aktiviert werden können [1]. In der Praxis ist das jedoch nur wenig sinnvoll, da so nicht sichergestellt werden kann, dass das Routing des partiell rekonfigurierbaren Blocks auch tatsächlich die Vorgaben an die Fence und das Trusted Routing einhalten.

Werden IDF und PR aktuell in Vivado 2018.2 im selben Design auf unterschiedliche Wrapper aktiviert, zeigt sich in der Praxis, dass der IDF einfach überstimmt wird und sich keine Isolation ausprägt (vgl. Abbildung 5).

Abbildung 4: Fehler bei IDF und PR beim selben Wrapper.

Auf Nachfrage teilte Xilinx mit, dass IDF und PR zwar im gleichen Design, jedoch nicht beim gleichen Wrapper aktiviert werden können [1]. In der Praxis ist das jedoch nur wenig sinnvoll, da so nicht sichergestellt werden kann, dass das Routing des partiell rekonfigurierbaren Blocks auch tatsächlich die Vorgaben an die Fence und das Trusted Routing einhalten.

Werden IDF und PR aktuell in Vivado 2018.2 im selben Design auf unterschiedliche Wrapper aktiviert, zeigt sich in der Praxis, dass der IDF einfach überstimmt wird und sich keine Isolation ausprägt (vgl. Abbildung 5).

Abbildung 5: Bei Zynq 7000 und auch Zynq UltraScale+ deaktiviert die partielle Rekonfiguration den IDF.

2.1 IDF und PR vereinen

Die Firma HTV führte in 2017 und 2018 umfang-reiche Untersuchung durch, wie IDF und PR dennoch für Zynq 7000 und Zynq UltraScale+ vereint werden können.

IDF und PR sind dann im gleichen Design kombinierbar, wenn ein isoliertes statisches Design erzeugt wird, in das anschließend ein partieller Bitstrom aus einem separaten partiell rekonfigurierbaren Projekt geladen wird. Dies ist über spezielle Zusatzsoftware möglich.

3. Fazit

Aktuell können in Vivado 2018.2 IDF und PR sowohl bei Zynq 7000 als auch Zynq UltraScale+ nur separat auf eine Design angewandt werden. Eine Verknüpfung beider Design Flows ist aktuell nicht sinnvoll möglich. Für den Zynq UltraScale+ soll es ab Vivado 2019.2 möglich sein. Für Zynq 7000 nie.

Über eine Zusatzsoftware ist HTV aber in der Lage, sowohl für Zynq 7000 als auch Zynq UltraScale+ isolierte statische Designs zu erzeugen in die später partielle Blöcke nachgeladen werden können.

Abbildung 5: Bei Zynq 7000 und auch Zynq UltraScale+ deaktiviert die partielle Rekonfiguration den IDF.

2.1 IDF und PR vereinen

Die Firma HTV führte in 2017 und 2018 umfang-reiche Untersuchung durch, wie IDF und PR dennoch für Zynq 7000 und Zynq UltraScale+ vereint werden können.

IDF und PR sind dann im gleichen Design kombinierbar, wenn ein isoliertes statisches Design erzeugt wird, in das anschließend ein partieller Bitstrom aus einem separaten partiell rekonfigurierbaren Projekt geladen wird. Dies ist über spezielle Zusatzsoftware möglich.

3. Fazit

Aktuell können in Vivado 2018.2 IDF und PR sowohl bei Zynq 7000 als auch Zynq UltraScale+ nur separat auf eine Design angewandt werden. Eine Verknüpfung beider Design Flows ist aktuell nicht sinnvoll möglich. Für den Zynq UltraScale+ soll es ab Vivado 2019.2 möglich sein. Für Zynq 7000 nie.

Über eine Zusatzsoftware ist HTV aber in der Lage, sowohl für Zynq 7000 als auch Zynq UltraScale+ isolierte statische Designs zu erzeugen in die später partielle Blöcke nachgeladen werden können.

Autor: © Halbleiter-Test & Vertriebs-GmbH

Der Isolation Design Flow fügt einem bestehenden Design nachträglich isolierte Zonen hinzu, die entweder gar nicht oder nur über ein spezielles "Trusted Routing" miteinander kommunizieren.

Abbildung 1: Regionen in einem FPGA werden durch physikalische Grenzen voneinander getrennt. Nur Verbindungen, die die Vorgaben des Trusted Routings einhalten, dürfen durch die festgelegten Grenzen verlaufen.

Für den IDF muss bei einem Blockdesign zunächst mit Wrappern eine Hierarchie erzeugt werden. Bei den Wrappern wird anschließend die Eigenschaft HD.ISOLATED aktiviert und für die Platzierung der Logik spezielle PBlöcke vorgegeben, die einen Mindestabstand von einem Tile aufweisen müssen.

Nach einer zusätzlichen Sperrung aller Logikelemente und Switchboxen zwischen den PBlöcken in der sogenannten Fence, bildet Vivado das Trusted Routing als direkte Verbindungen ohne Abzweige zwischen den PBlöcken aus (vgl. Abbildung 1).

1.1 Aktueller Stand beim VIV

Der Isolation Design Flow fügt einem bestehenden Design nachträglich isolierte Zonen hinzu, die entweder gar nicht oder nur über ein spezielles "Trusted Routing" miteinander kommunizieren.

Abbildung 1: Regionen in einem FPGA werden durch physikalische Grenzen voneinander getrennt. Nur Verbindungen, die die Vorgaben des Trusted Routings einhalten, dürfen durch die festgelegten Grenzen verlaufen.

Für den IDF muss bei einem Blockdesign zunächst mit Wrappern eine Hierarchie erzeugt werden. Bei den Wrappern wird anschließend die Eigenschaft HD.ISOLATED aktiviert und für die Platzierung der Logik spezielle PBlöcke vorgegeben, die einen Mindestabstand von einem Tile aufweisen müssen.

Nach einer zusätzlichen Sperrung aller Logikelemente und Switchboxen zwischen den PBlöcken in der sogenannten Fence, bildet Vivado das Trusted Routing als direkte Verbindungen ohne Abzweige zwischen den PBlöcken aus (vgl. Abbildung 1).

1.1 Aktueller Stand beim VIV

Ob die Isolation erfolgreich durchgeführt werden konnte, kann mit dem VIV (Vivado Isolation Verifier) überprüft werden.

Dieser musste in Vivado 2017.2 noch als separates Script nachgeladen werden und existierte hier nur für den Zynq 7000.

In Vivado 2018.2 ist der VIV fester Bestandteil im Design Rule Check (DRC) und muss nur über den Befehl set_param hd.enableIDFDRC true aktiviert werden. Nach der Implementation stehen dann zusätzliche Prüfungen im DRC im Bereich der Isolation zur Verfügung (vgl. Abbildung 2).

Abbildung 2: Aktivierung des VIV im DRC.

2. Partielle Rekonfiguration und Isolation Design Flow

Ob die Isolation erfolgreich durchgeführt werden konnte, kann mit dem VIV (Vivado Isolation Verifier) überprüft werden.

Dieser musste in Vivado 2017.2 noch als separates Script nachgeladen werden und existierte hier nur für den Zynq 7000.

In Vivado 2018.2 ist der VIV fester Bestandteil im Design Rule Check (DRC) und muss nur über den Befehl set_param hd.enableIDFDRC true aktiviert werden. Nach der Implementation stehen dann zusätzliche Prüfungen im DRC im Bereich der Isolation zur Verfügung (vgl. Abbildung 2).

Abbildung 2: Aktivierung des VIV im DRC.

2. Partielle Rekonfiguration und Isolation Design Flow

Die partielle Rekonfiguration bezeichnet den Vorgang bei dem die Inhalte eines PBlocks in einem FPGA-Design im laufenden Betrieb nachgeladen werden.

Auf ein bestehendes Blockdesign kann ein spezieller TCL Flow angewandt werden, um die benötigten partiellen und statischen Bitströme zu einem Design zu erzeugen. Xilinx verkündet offiziell auf seiner Webseite, dass es möglich ist, den Isolation Design Flow und die partielle Rekonfiguration im selben Design zu vereinen.

Der praktische Test zeigt, dass beim selben Design beim selben Wrapper die Eigenschaft HD.ISOLATED und die Eigenschaft HD.RECONFIGRUABLE gleichzeitig aktiviert werden können (vgl. Abbildung 3).

Abbildung 3: Aktivierung von IDF und PR beim selben Wrapper.

Der DRC führt bei der gleichzeitigen Aktivierung jedoch zu einer Fehlermeldung und die Implementation kann nicht fehlerfrei durchgeführt werden (vgl. Abbildung 4).

Die partielle Rekonfiguration bezeichnet den Vorgang bei dem die Inhalte eines PBlocks in einem FPGA-Design im laufenden Betrieb nachgeladen werden.

Auf ein bestehendes Blockdesign kann ein spezieller TCL Flow angewandt werden, um die benötigten partiellen und statischen Bitströme zu einem Design zu erzeugen. Xilinx verkündet offiziell auf seiner Webseite, dass es möglich ist, den Isolation Design Flow und die partielle Rekonfiguration im selben Design zu vereinen.

Der praktische Test zeigt, dass beim selben Design beim selben Wrapper die Eigenschaft HD.ISOLATED und die Eigenschaft HD.RECONFIGRUABLE gleichzeitig aktiviert werden können (vgl. Abbildung 3).

Abbildung 3: Aktivierung von IDF und PR beim selben Wrapper.

Der DRC führt bei der gleichzeitigen Aktivierung jedoch zu einer Fehlermeldung und die Implementation kann nicht fehlerfrei durchgeführt werden (vgl. Abbildung 4).

Abbildung 4: Fehler bei IDF und PR beim selben Wrapper.

Auf Nachfrage teilte Xilinx mit, dass IDF und PR zwar im gleichen Design, jedoch nicht beim gleichen Wrapper aktiviert werden können [1]. In der Praxis ist das jedoch nur wenig sinnvoll, da so nicht sichergestellt werden kann, dass das Routing des partiell rekonfigurierbaren Blocks auch tatsächlich die Vorgaben an die Fence und das Trusted Routing einhalten.

Werden IDF und PR aktuell in Vivado 2018.2 im selben Design auf unterschiedliche Wrapper aktiviert, zeigt sich in der Praxis, dass der IDF einfach überstimmt wird und sich keine Isolation ausprägt (vgl. Abbildung 5).

Abbildung 4: Fehler bei IDF und PR beim selben Wrapper.

Auf Nachfrage teilte Xilinx mit, dass IDF und PR zwar im gleichen Design, jedoch nicht beim gleichen Wrapper aktiviert werden können [1]. In der Praxis ist das jedoch nur wenig sinnvoll, da so nicht sichergestellt werden kann, dass das Routing des partiell rekonfigurierbaren Blocks auch tatsächlich die Vorgaben an die Fence und das Trusted Routing einhalten.

Werden IDF und PR aktuell in Vivado 2018.2 im selben Design auf unterschiedliche Wrapper aktiviert, zeigt sich in der Praxis, dass der IDF einfach überstimmt wird und sich keine Isolation ausprägt (vgl. Abbildung 5).

Abbildung 5: Bei Zynq 7000 und auch Zynq UltraScale+ deaktiviert die partielle Rekonfiguration den IDF.

2.1 IDF und PR vereinen

Die Firma HTV führte in 2017 und 2018 umfang-reiche Untersuchung durch, wie IDF und PR dennoch für Zynq 7000 und Zynq UltraScale+ vereint werden können.

IDF und PR sind dann im gleichen Design kombinierbar, wenn ein isoliertes statisches Design erzeugt wird, in das anschließend ein partieller Bitstrom aus einem separaten partiell rekonfigurierbaren Projekt geladen wird. Dies ist über spezielle Zusatzsoftware möglich.

3. Fazit

Aktuell können in Vivado 2018.2 IDF und PR sowohl bei Zynq 7000 als auch Zynq UltraScale+ nur separat auf eine Design angewandt werden. Eine Verknüpfung beider Design Flows ist aktuell nicht sinnvoll möglich. Für den Zynq UltraScale+ soll es ab Vivado 2019.2 möglich sein. Für Zynq 7000 nie.

Über eine Zusatzsoftware ist HTV aber in der Lage, sowohl für Zynq 7000 als auch Zynq UltraScale+ isolierte statische Designs zu erzeugen in die später partielle Blöcke nachgeladen werden können.

Abbildung 5: Bei Zynq 7000 und auch Zynq UltraScale+ deaktiviert die partielle Rekonfiguration den IDF.

2.1 IDF und PR vereinen

Die Firma HTV führte in 2017 und 2018 umfang-reiche Untersuchung durch, wie IDF und PR dennoch für Zynq 7000 und Zynq UltraScale+ vereint werden können.

IDF und PR sind dann im gleichen Design kombinierbar, wenn ein isoliertes statisches Design erzeugt wird, in das anschließend ein partieller Bitstrom aus einem separaten partiell rekonfigurierbaren Projekt geladen wird. Dies ist über spezielle Zusatzsoftware möglich.

3. Fazit

Aktuell können in Vivado 2018.2 IDF und PR sowohl bei Zynq 7000 als auch Zynq UltraScale+ nur separat auf eine Design angewandt werden. Eine Verknüpfung beider Design Flows ist aktuell nicht sinnvoll möglich. Für den Zynq UltraScale+ soll es ab Vivado 2019.2 möglich sein. Für Zynq 7000 nie.

Über eine Zusatzsoftware ist HTV aber in der Lage, sowohl für Zynq 7000 als auch Zynq UltraScale+ isolierte statische Designs zu erzeugen in die später partielle Blöcke nachgeladen werden können.Autor: © Halbleiter-Test & Vertriebs-GmbH